1. FPGA可以运行几个固件

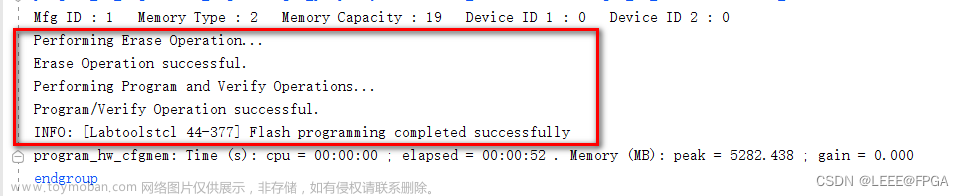

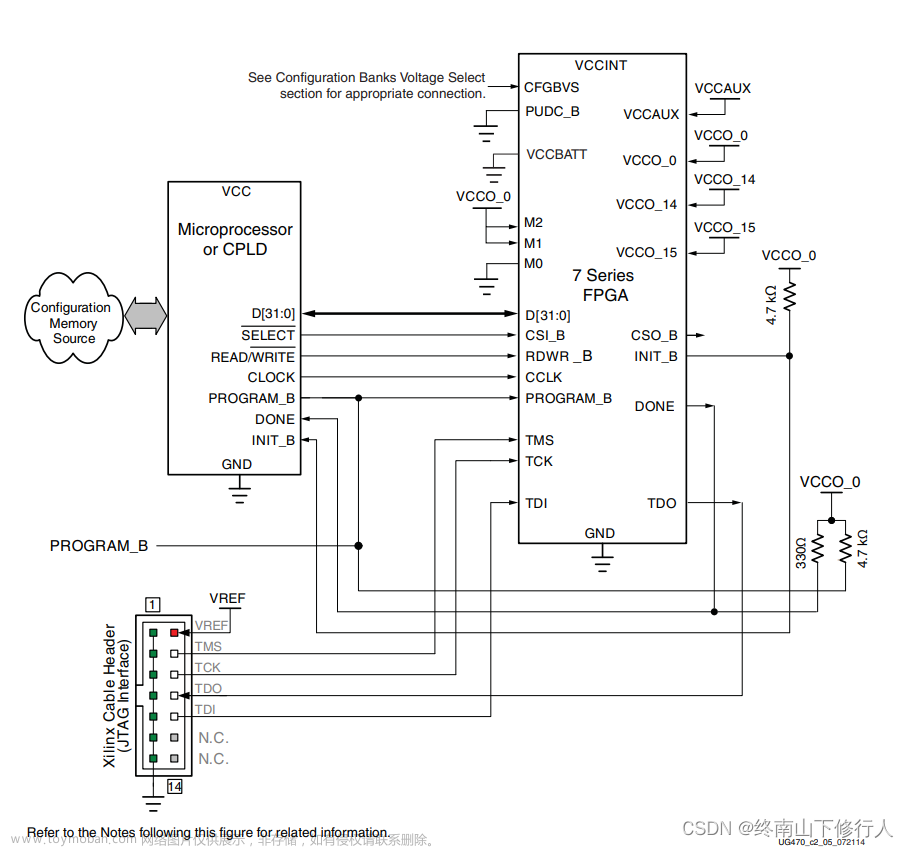

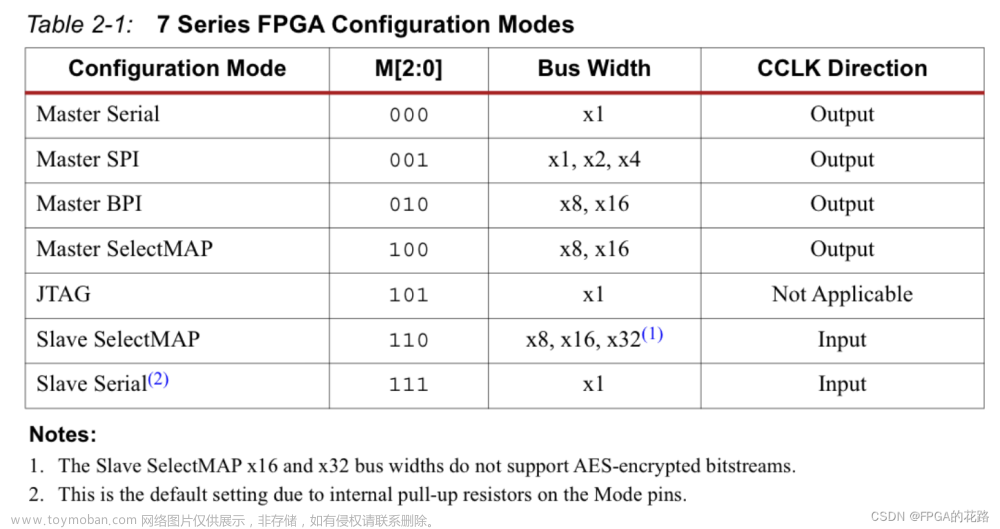

众所周知,常见的FPGA通常为SRAM结构,固件程序一般存放在外置的串行Flash中,比如SPI Flash,M25P16或N25Q128等。

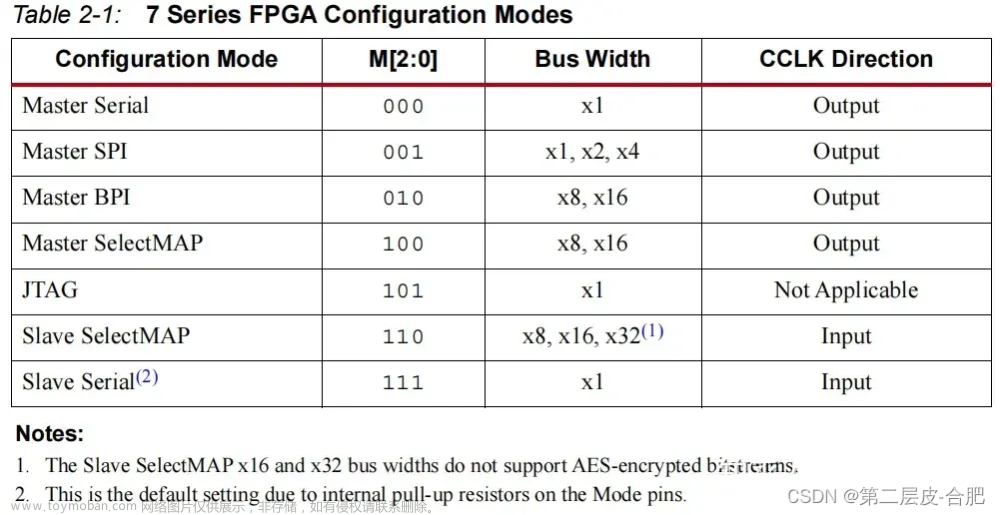

FPGA启动时,一般先从SPI起始地址开始加载数据到内部的SRAM,加载完成、校验通过则会直接运行。

那么有没有可能在SPI Flash中存放两个或多个FPGA固件呢?

FPGA同时只能运行一个固件,那么是否可以在运行过程中,通过某种方式切换到另一个固件呢?文章来源:https://www.toymoban.com/news/detail-432524.html

答案是可以的,对于Xilinx的FPGA产品来说,可以通过ICAP原语来实现!可以做到存放多个固件程序,应用场景也比较广泛,比如固件升级方案中,Bootloader存放文章来源地址https://www.toymoban.com/news/detail-432524.html

到了这里,关于Xilinx FPGA ICAP原语实现多重配置的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!