开发板:正点原子达芬奇FPGA开发板

芯片型号:Xilinx Artix-7 35T

开发工具:Vivado 2022.1

源码链接:e203_hbirdv2: The Ultra-Low Power RISC-V Corehttps://gitee.com/riscv-mcu/e203_hbirdv2?_from=gitee_search

发现IP有报错:

此时,打开system.v文件 ,发现IP名不对,所以我们要重新设置IP

所以我们来修改第一个IP:

单击IP Catalog,搜索clk,双击Clocking Wizard,将clk_wiz_0改为mmcm,达芬奇开发板上只有一个50MHz时钟源,进行一个更改:

我们需要一个16MHz时钟,利用MMCM将50MHz时钟源降频为 16MHz :

注意将system.v文件 中mmcm中的clk_out2改为clk_out1,设置完成后,Generate

此外,我们还需要一个32.768KHz时钟,32.768KHz由于频率过低无法通过此IP实现,需要自己写分频器 ,具体步骤为新建一个.v文件,将如下代码复制粘贴,将其例化进system.v文件:

//50MHz --> 32768Hz 约为1526倍 50MHz/1526=32765.4 HZ,作为常开域时钟

module clk_div(

input CLK50MHZ,

input rst_n,

output reg clk_div

);

parameter NUM_DIV = 11'd1526;

reg [10:0] cnt;

always @(posedge CLK50MHZ or negedge rst_n)

if(!rst_n) begin

cnt <= 11'd0;

clk_div <= 1'b0;

end

else if(cnt < NUM_DIV / 2 - 1) begin

cnt <= cnt + 1'b1;

clk_div <= clk_div;

end

else begin

cnt <= 11'd0;

clk_div <= ~clk_div;

end

endmodule

注意将系统时钟由CLK100MHZ 改为CLK50MHZ

修改第二个ip设置,单击IP Catalog,搜索reset,双击Processor System Reset,将proc_sys_reset_0改为reset_sys:

修改第二个ip设置,单击IP Catalog,搜索reset,双击Processor System Reset,将proc_sys_reset_0改为reset_sys:

设置完成后,Generate

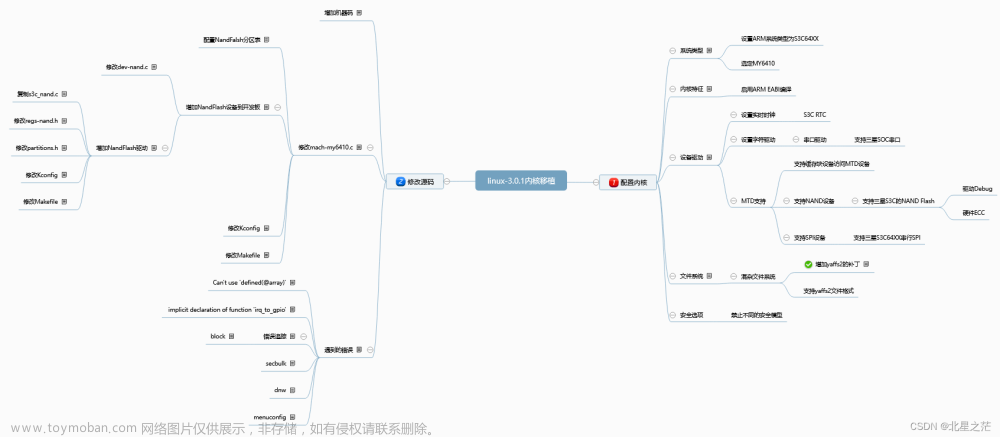

最终结果如下图:

文章来源:https://www.toymoban.com/news/detail-432698.html

文章来源:https://www.toymoban.com/news/detail-432698.html

文章来源地址https://www.toymoban.com/news/detail-432698.html

到了这里,关于移植蜂鸟E203内核至达芬奇pro35T【集创芯来RISC-V杯】(二)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!