提高存储器访问层次大概有三种方法

-

采用高速器件

-

采用层次结构 Cache 主存

-

调整主存结构

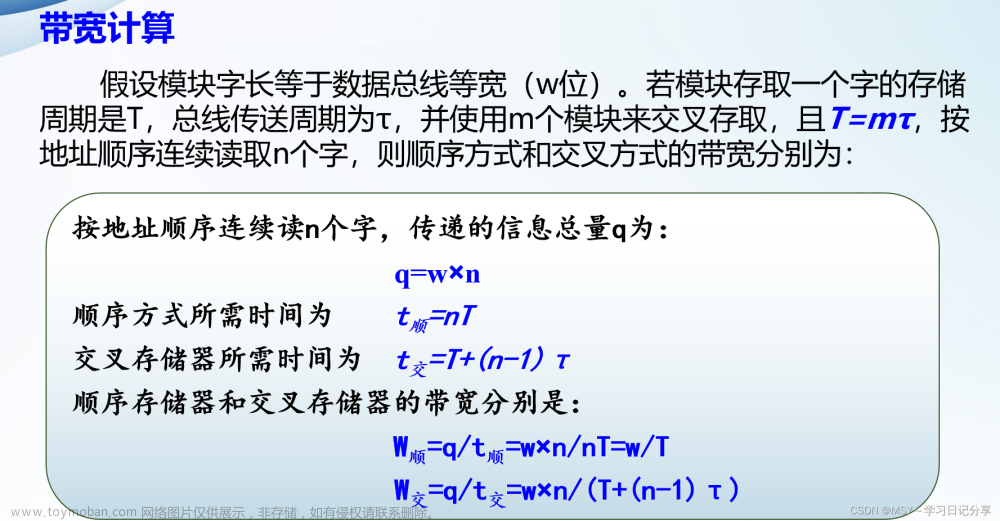

调整存储结构

单体多字系统

利用程序局部性原理,访问一个块 相邻的若干块都会被拿出来,缺点可能会碰到跳转类指令

多体并行系统

文章来源:https://www.toymoban.com/news/detail-432902.html

文章来源:https://www.toymoban.com/news/detail-432902.html高位是体号,低位时地址因此,CPU给出一次存储访问总是对一块连续的存储单元进行的,在多CPU系统中,不同的CPU访问不同的存储块,达到并行工作。文章来源地址https://www.toymoban.com/news/detail-432902.html

到了这里,关于计算机组成原理4.2.3提高存储器访问速度的措施的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!