CSI(Camera Serial Interface)是由MIPI联盟下Camera工作组指定的接口标准。CSI-2是MIPI CSI第二版,是一个单或双向差分串行界面,包含时钟和数据信号。主要由应用层、协议层、物理层组成,最大支持4通道(Lane)数据传输、单线传输速度高达1Gb/s。

MIPI CSI2的分层方法有好几种,根据MIPI联盟的规范,CSI-2大致分为三层,分别为:应用层、协议层、物理层。协议层再分为三层:像素/字节组包/解包层、底层协议层、通道管理层。

一、应用层(Application Layer)

这一层描述了比CSI-2协议描述的更高层级得编码和解释方式,与CSI-2协议本身关系不大。

二、协议层(Protocol Layer)

1. 像素/字节打包/解包层(Pixel/Byte Packing/Unpacking Layer)

支持多种像素格式的图像传输。发送端会将从应用层传下来的像素数据打包成字节流传递给底层协议层,接收端将从底层协议层传递的字节进行解包并发送给应用层。

以RAW10格式的图像数据为例,一个像素占10bit,pack的过程为:每个像素抽出2bit,剩下的8bit的作为一个字节传输;每4个像素抽出的2bit组合成一个字节传输。因此4个像素使用5个字节传输,这就是像素流转换成字节流的过程。

因此,RAW10数据packed后数据流如下图。

CSI-2协议官方文档中也提供了其他形式的图像的pack方法。

RGB888的打包方式

RGB666的打包方式。

YUV422 10bit的打包方式。

更多格式可以阅读MIPI CSI-2官方文档,此处不再举例。

2. 底层协议层(Low Level Protocol, LLP)

LLP层通常会处理两种格式的包(Packet):长包(Long Packet)和短包(Short Packet)。无论哪一种包,LLP层都会根据CSI-2协议的规定,给它们添加包头(Packet Header, PH)和包尾(Packet Footer, PF),并作为有效数据在HS模式下传输。

同时,LLP层会在每次退出LP后添加一个SoT(Start of Transmission)序列作为开始进入HS模式的标志,并在进入LP模式前添加一个EoT(End of Transmission)序列作为退出HS模式的标志。如下图所示。

长包结构

D-PHY

如果物理层选用D-PHY时,则长包中主要包括三个部分:32bit的PH、一定长度的packet data和8bit的PF。具体结构如下图。

- 数据标识(DI) :总共8bit。由VC(2bit)字段和DT(6bit)字段构成,VC字段表示VC id的低两位,DT代表packet layer的数据类型。

- 数据计数(WC) :总共16bit。从PH结尾到PF起始位置中间的填充数据的长度,也就是packet data的长度。单位为字节。接收端可以通过WC来判断包的结尾位置。

- 虚拟通道拓展+错误校验码(VCX+ECC):总共8bit。其中,ECC占6bit,采用Hamming Code,可以纠正PH中DI+WC+VCX中的一位错误或发现两位错误;VCX占2bit,代表VC id的高两位,与DI中的VC一起组成4-bit的VC id,总共能表示16个虚拟通道。

- 数据填充(Data Payload,或称为Packet Data) :长度=WC*8bits。因为WC的存在,接收端可以直接通过WC来判断包尾在什么位置,因此不需要在传输的数据中内嵌标志位等用来同步的信号。也就是说LLP层对具体的数据内容没有任何限制。

- 检验和(CS):总共16bit。CHECKSUM采用CCITT的16-bit的CRC校检,用来校验packet data中的错误,即x16+x12+x5+x0。CRC只能检测出一个或者多个错误,并不能纠正错误。

C-PHY

如果物理层选用C-PHY时,则包括PH、packet data、PF、填充字节FILLER四个部分。具体结构如下图。

如果C-PHY物理层有N个lane,则PH由以下字段构成

- RES+VCX:总共8 bit,由5-bit RES + 3-bit VCX构成。RES是保留位,暂时没有用处,都置为0。VCX是VC id的最高三位,与DI中的VC字段共同构成5-bit的VC id,总共能代表32个虚拟通道。

- DI:总共8 bit。与D-PHY的DI字段含义相同,包括2bit的VC,代表VC id的低两位;还有6bit的DT,代表packet data的数据类型。

- WC:总共16 bit。与D-PHY的WC字段含义相同,接收端读取WC的值来决定packet data的结尾。

- PH-CRC:总共16 bit。使用CRC校验方式对PH进行校验(RES+VCX+DI+WC),可以检测出多bit的错误。

- 发送完上述字段后,C-PHY物理层会插入一个同步字(Sync Word),作为CSI-2 PPI(PHY Protocol Interface)指令的执行结果。

- 然后会再复制一份上述的RES+VCX、DI、WC、PH-CRC的数据放在PH中。因此总共的长度为6×16bits,这是一个lane的PH字段构成。如果物理层有N个lane,则重复N次上述字段,因此PH的总长度为6N×16bits。

PH中的每6个16-bits数据会被广播到N条lane上,这6个word还会继续每3word一组分成两部分,C-PHY物理层会在两者间插入sync word,用于响应CSI-2 Tx的PPI命令。如下图所示。

PF由16 bit的CRC校验计算得到,作用与D-PHY中的相同。

Packet Filler在PF后插入。一般它的值取为0。包含两个作用:

- PF需要填充对齐时,Filler部分的字节会被插入到PF后来保证16 bit对齐。即如果WC是一个奇数,则CSI-2发送端会在PF后插入1字节的Packet Filler,保证PF是以16bit为单位结束的。

- 插入额外的Filler字节,以保证每个C-PHY的每个lane都传输相同数量的16 bit字。

综上,对于两种形式的物理层实现,总结如下:

- DI字段:均包括一个8bit的DI字段,由2 bit的VC和6 bit的DT构成。均包括VCX字段,用于扩展VC id的大小,但D-PHY的VCX为2bit,C-PHY为3bit。

- WC字段:均包括一个16bit的WC字段,用来确定Packet Data的长度。注意两点:(1)WC的单位是字节数(2)只统计PH到PF之间的有效数据的长度。

- ECC字段:对于D-PHY,6bit的ECC校验码用来校验PH中的DI+WC+VCX字段,能够纠正1bit错误并检测出2bit的错误。

对于C-PHY,没有ECC字段,这是由于在C-PHY物理层链路上如果发生了一个单符号错误会导致接收到的包头PH里有多bit错误出现,因此ECC字段不再有用。作为替代,CSI-2协议中对C-PHY使用一个16bit的CRC字段,用来校验RES+VCX+DT+WC,并将这些字段连同CRC字段一起复制多份发送出去,因此接收端可以发现1个或多个物理层链路上的传输错误并恢复。同时,C-PHY物理层会在PH中加入同步字,使得C-PHY接收端时钟信号也丢失的情况下恢复PH数据。 - Data Payload:接收端均通过读取PH中的WC字段来判断Data Payload的长度,这个过程中接收端显然是无需寻找任何用作数据同步的编码的,因此Data Payload只需要保证自己以8bit为单位即可,对其内容没有任何限制。

- CRC字段:接收端一旦接收完Data Payload后,均开始接收并校验PF中的checksum字段,同时自己计算也根据接收的数据计算checksum并比较,以判断传输过程中是否出现错误。

- FILLER字段:只在C-PHY中使用,上文中已详尽叙述过。

短包结构

下图分别展示了D-PHY的短包结构和C-PHY的短包结构。无论采用哪种物理层结构,短帧结构相当于只有长帧结构中的PH,没有PF和中间的数据域。PH中依旧包括DI、WC、ECC三个部分,其中,DI和ECC含义与长帧结构中的相同,DI中依旧包括VC和DT,只不过DT只使用上面的Data Type表格中的0x00 ~ 0x0F这一范围。

短帧结构中的WC域用作短帧的数据域(Data Field),具体含义为:如果该短帧的Data Type为帧同步(Frame Synchronization),则数据域表示帧数;如果短帧的Data Type为行同步(Line Synchronization),则数据域表示行数。

Virtual Channel虚拟通道

所谓的虚拟通道,是一种逻辑上的通道,不同格式的数据可以在同一个物理通道上交织传输,也就是在同一条lane上交织传输,为了让接收端能够区分出不同的数据流,需要在数据帧前面加上VC ID(Virtual Channel Identifier),接收端根据VC ID区分出该数据帧属于哪个逻辑通道并将数据包重新组合。

CSI-2协议中,VC ID的低2位来自DI的VC字段,高2位(针对D-PHY)或高3位(针对C-PHY)来自VCX字段,因此D-PHY和C-PHY支持的最大虚拟通道数为16或32。早期的CSI-2不支持VCX字段,对于这样的主处理器,会将VCX当作全零。

下图是交织视频流传输示意图。使得CSI-2可以在同一个Lane发送不同类型的数据,然后在接收端在进行恢复。接收端在同一个Lane上接收到交织传输的不同数据流,需要通过每个数据帧中包含VC ID来区分出各个数据流所属的逻辑上的通道。下图中,三个数据Lane上交叉传输了Virtual Channel 0和Virtual Channel 1的数据。其中,VC0上传输的是RGB666格式的数据,VC1上传输的是YUV422格式的数据。三路Data Lane在接收到数据后,会根据VC的ID将数据进行重新组合,得到两张图像。

虚拟通道会在什么场景下使用到呢?这里举个例子。索尼推出的支持DOL-HDR算法的sensor,长曝光和短曝光的两帧是同时一次卷帘曝光中同时得到的,也就是所谓的行交织的曝光方式。因此,在MIPI tx中长曝光帧和短曝光帧按行交叉传输出来,后续的图像处理模块如何得知某一行是属于长曝光帧还是短曝光帧呢?就是通过vc来进行区分。例如,给长曝光帧vc设为0,短曝光帧的vc设为1(通常在sensor中是可配的),那么接收端就可以通过不同的vc将两帧重组。

关于HDR算法是什么,可以阅读这篇文章进行了解。

Data Type数据类型

Data Type指明了payload data的数据格式和内容,最多支持64种数据格式。

如下表,共有八大类不同的data type,每一类下面定定义了至多九种不同的data type。前两个类别(0x00 ~ 0x0F)是适用于短包的data type,剩下六个类别(0x10~0x38)是适用于长包的data type。

下表为Synchronization Short Packet的Data Type具体编码。Synchronization Short Packet顾名思义,就是用做帧同步或行同步的短包。

下表为Generic Short Packet(通用短包)的Data Type编码。这一部分的作用是为打开/关闭快门、触发闪光灯等操作的时序信息等提供一个数据传输的机制。通用短包中的Data Type编码和16bit数据域的编码都是用户自定义的,发送端会从发送端应用层接收这两个数据并发送给接收端,接收端收到后会将二者传递给接收端应用层。

下表为通用长包的数据类型定义。

- Null或Blanking Data类型代表接收端需要忽略包内Payload data的内容。Null Packet表示改数据包完全无意义,Blanking Packet则在ITU-R BT.656风格的视频流中可能会用来表示帧间的blanking lines。

- Embedded Data表示每个图像帧开始或结束位置加入的额外信息。

- 通用长包类型1~4:可以由用户自定义,例如可以用来识别不同类型的元数据包。

下表为YUV图像格式的数据类型。其中,YUV420格式包含legacy和非legacy两类,前者是为了兼容一些已有的系统,后者是为了减小实现开销。后续我们会对YUV格式做更具体的介绍。

下表为RGB图像格式的数据类型。

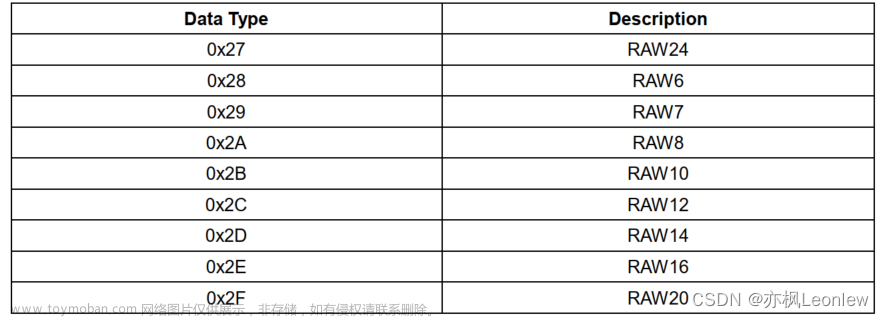

下表为RAW图像格式的数据类型。这些图像通常是从sensor中输出的未经处理的图像数据(如Raw Bayer数据),或互补色图像数据,但RAW图像不限于这些类型。

三、通道管理层

CSI-2是一个可扩展lane协议,相比只有一个Data Lane的传输方式,使用多个Data Lane可以在相对更低的时钟频率下传输更多数据。高层级的数据流映射到多条Lane

上的方式需要被严格规定,以便不同种类的host设备和外设在使用这种多Lane传输方式时可以兼容。

通过管理层就是用来处理多Lane的配置工作的。如下图所示,无论物理层选用C-PHY还是D-PHY,在CSI-2发射端,会使用一个Lane Distribution Function(LDF)将从LLP层收到的一系列Packet分发给N条Lane上,每个Lane都是一个独立的物理层逻辑单元加传输电路。

D-PHY的LDF

C-PHY的LDF。

同理,接收端使用Lane Merging Function(LMF)将从N条Lane上收集的数据合并成一个完整的Packet并传递给接收端的LLP层进行解码。

D-PHY的LMF。

C-PHY的LMF。 文章来源:https://www.toymoban.com/news/detail-433419.html

文章来源:https://www.toymoban.com/news/detail-433419.html

三、物理层

物理层用来实际的连接发送端和接收端,并将数字信号转换成模拟信号真正传输出去。常见的物理层协议有D-PHY、C-PHY和M-PHY。更详细的内容可以阅读我的前两篇文章,此处不再赘述。

MIPI简介(一)——基础概念介绍

MIPI简介(二)——物理层D-PHY文章来源地址https://www.toymoban.com/news/detail-433419.html

到了这里,关于MIPI简介(三)——CSI-2的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!