写在前面

本科时学过FPGA的相关课程,因此对于Verilog相关语法的学习重在回顾。

1.Verilog的数据类型

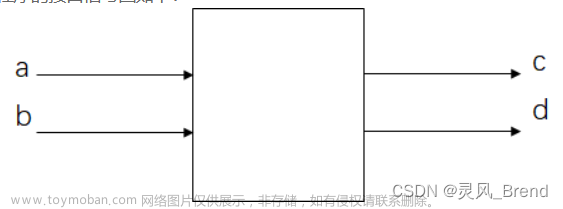

Verilog 最常用的 2 种数据类型就是线(wire)与寄存器(reg),其余类型可以理解为这两种数据类型的扩展或辅助。

1.1wire类型

wire 类型表示硬件单元之间的物理连线,由其连接的器件输出端连续驱动。

线类型可以由寄存器类型来赋值;

//以下为位宽为1的情况

wire flag; //声明1bit位宽的线型变量data

reg wr_load_r1, wr_load_r2;

wire flag1 = ~wr_load_r2 & wr_load_r1;

//当位宽大于1时

wire [23:0] data; //声明24bit位宽的线型变量data

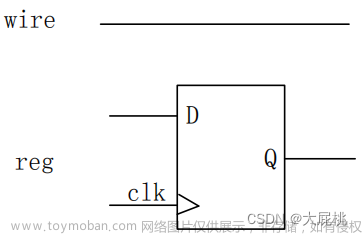

1.2reg类型

寄存器用来表示存储单元,它会保持数据原有的值,直到被改写。寄存器不需要驱动源,也不一定需要时钟信号。在仿真时,寄存器的值可在任意时刻通过赋值操作进行改写。

//以下为位宽为1的情况

reg rd_addr;

reg wr_addr;

reg rstn ;

initial begin

rstn = 1'b0 ;

#100 ;

rstn = 1'b1 ;

end

//当位宽大于1时

reg [3:0] counter ; //声明4bit位宽的寄存器counter

1.3[X:0]和[0:X]的区别

不管是reg变量还是wire变量,A[X:0],A[X]是最高位,A[0]是最低位。B[0:X],B[0]是最高位,B[X]是最低位。

例如声明了两个8位的寄存器变量data1和data2,并对这两个寄存器变量赋值8‘b11110000。

reg [7:0] data1;

reg [0:7] data2;

reg [7:0] data;

data1 = 8'b00000000;

data2 = 8'b00000000;

data1 <= data;

data2 <= data;

这时

data1[7]=1, data1[6]=1, data1[5]=1, data1[4]=1, data1[3]=0, data1[2]=0, data1[1]=0, data1[0]=0;

data2[0]=1, data2[1]=1, data2[2]=1, data2[3]=1, data2[4]=0, data2[5]=0, data2[6]=0, data2[7]=0.

对于data1而言,data1[7]是最高位

对于data2而言,data2[0]是最高位

1.4parameter数据

parameter用来表示常量,用关键字 parameter 声明,只能赋值一次.

parameter data_width = 10'd32 ;

parameter i=1, j=2, k=3 ;

1.5一些骚操作

1.5.1花括号{}的使用

花括号{}的功能包括拼接和复制

拼接

wire [2:0] a;

在a的最高位再补一位填上1变成一个4位二进制串,那么我只需要用

{1’b1,a[2:0]}

就可以表示这个4位串了。其中最左边是最高位,最右边是最低位。如果a[2:0]=3’b011,{1’b1,a[2:0]}就等于4’b1011了。之所以要写1’b1而不是1,是因为在拼接运算符中,要求所有使用到的数和变量都要标明位数。

复制

{32{a[1]}}

其中32表示要把a[1]重复32次,并不是要拼接的内容,所以就不用指定位长了。比如a[1]=1,上面的描述就对应了一个长度为32,每一位都是1的二进制串。注意上面的表达式连同最外面的花括号是一个整体,意思就是说如果你想要把这个串嵌套在别的拼接运算符中时,最外面的花括号是不能删掉的

此外,关于我们的{32{a[1]}},其中重复的次数“32”可以替换成参数,即这个32可以替换成一个parameter类型,但不能替换成一个wire类型,reg类型甚至integer类型。

1.5.2数据的截取

Verillog支持指定 bit 位后固定位宽的向量域选择访问。

[bit+: width] : 从起始 bit 位开始递增,位宽为 width。

[bit-: width] : 从起始 bit 位开始递减,位宽为 width。文章来源:https://www.toymoban.com/news/detail-433704.html

//下面 2 种赋值是等效的

A = data1[31-: 8] ;

A = data1[31:24] ;

//下面 2 种赋值是等效的

B = data1[0+ : 8] ;

B = data1[0:7] ;

1.Verilog 数据类型

2.Verilog中拼接运算符的用法文章来源地址https://www.toymoban.com/news/detail-433704.html

到了这里,关于【FPGA学习记录3-1】Verilog语法之Verilog的数据类型的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Verilog数据类型/常量/变量[学习笔记day3]](https://imgs.yssmx.com/Uploads/2024/02/752968-1.png)