前言:

本文主要介绍了EDA原理与应用这门课程的相关实验及代码。使用的软件是Quartus Ⅱ,该实验使用fpga芯片为cycloneⅤ 5CSEMA5F31C6。

(一)实验目的

(1)熟悉交通灯控制器的工作原理;

(2)了解设计中的优化方案;

(3)进一步掌握状态机的设计;

(4)学习较复杂数字系统设计。

(二)设计要求

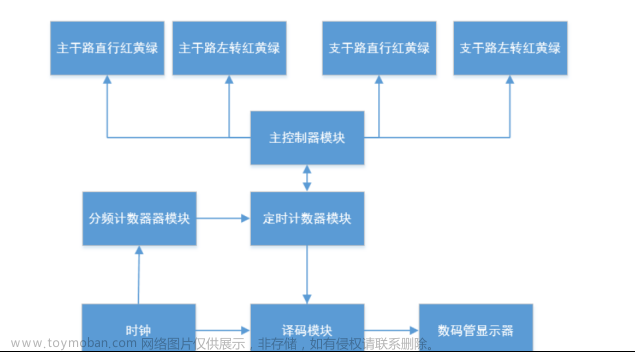

实现一个由一条主干道和一条乡间公路形成的十字路口的交通灯控制器功能:

(1)有MR(主红)、MY(主黄)、MG(主绿)、CR(乡红)、CY(乡黄)、CG(乡绿)六盏交通灯需要控制;

(2)交通灯由绿转红前有4秒亮黄灯的间隔时间,由红转绿没有间隔时间;

(3)乡间公路右侧各埋有一个串连传感器,当有车辆准备通过乡间公路时,发出请求信号S=1,其余时间S=0;

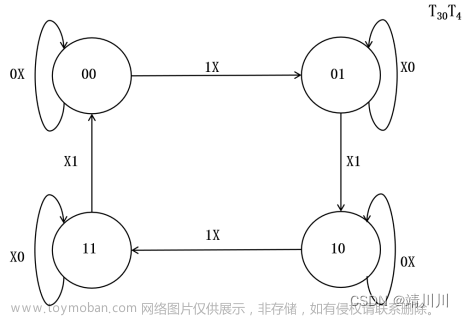

(4)平时系统停留在主干道通行(MGCR)状态,一旦S信号有效,经主道黄灯4秒(MYCR)状态后转入乡间公路通行(MRCG)状态,但要保证主干60s后才能转换;

(5)一旦S信号消失,系统脱离MRCG状态,即经乡道黄灯4秒(MRCY)状态进入MGCR状态,即使S信号一直有效,MRCG状态也不得长于20秒钟;

(三)实验代码文章来源:https://www.toymoban.com/news/detail-433960.html

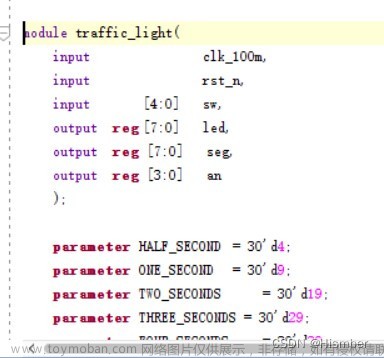

module jiaotongdeng(clk,s,rst,MG,CR,MY,MR,CG,CY,SG0,SG1,sw,gw,clk1,c);

input clk,rst,s;

output reg MG,CR,MY,MR,CG,CY; //主绿黄红,乡绿黄红

output gw,sw,clk1;

output reg [6:0] SG0,SG1;

output reg [5:0] c;

parameter s0=0,s1=1,s2=2,s3=3;

reg clk1;

reg [7:0] timCG,timMG,timY;

reg [7:0] tim;

reg [1:0] cs;

reg [1:0] next_state;

reg [30:0] cnt;

reg [7:0] a;

reg [3:0]gw,sw;

//分频器

//仿真

always @(posedge clk)

begin

cnt=cnt+1;

if(cnt>1) begin clk1=1'b1; cnt=0; end

else clk1=1'b0;

gw<=tim[3:0];

sw<=tim[7:4];

c[0]<=CY;c[1]<=CG;c[2]<=CR;

c[3]<=MY;c[4]<=MG;c[5]<=MR;

end

//跑板子,50MHZ-49999999

/*

always @(posedge clk)

begin

cnt=cnt+1;

if(cnt>49999999) begin clk1=1'b1; cnt=0; end

else clk1=1'b0;

gw<=tim[3:0];

sw<=tim[7:4];

c[0]<=CY;c[1]<=CG;c[2]<=CR;

c[3]<=MY;c[4]<=MG;c[5]<=MR;

end

*/

//CS状态选择

always@(cs)

case(cs)

s0:if(tim=='b0&&s=='b1) next_state<=s1; else next_state<=s0;

s1:if(tim=='b0) next_state <=s2; else next_state<=s1;

s2:if(tim=='b0||s==0) next_state<=s3; else next_state<=s2;

s3:if(tim=='b0) next_state<=s0; else next_state<=s3;

default: next_state<=s0;

endcase

//复位

always@(posedge clk1 or negedge rst)

begin

if(!rst)

cs<=s0;

else

cs<=next_state;

end

//cs-->此时状态

always@(negedge clk1)

case(cs)

s0:begin MY<='b0;MG<='b1;MR<='b0;CG<='b0;CY<='b0;CR<='b1;end //主绿乡红

s1:begin MY<='b1;MG<='b0;MR<='b0;CG<='b1;CY<='b0;CR<='b0;end //主黄乡绿

s2:begin MY<='b0;MG<='b0;MR<='b1;CG<='b1;CY<='b0;CR<='b0;end //主红乡绿

s3:begin MY<='b0;MG<='b0;MR<='b1;CG<='b0;CY<='b1;CR<='b0;end //主红乡黄

default:begin MY<='b0;MG<='b1;MR<='b1;CG<='b0;CY<='b0;CR<='b0;end

endcase

//判断

always@(negedge clk1,negedge rst)

if(!rst)

begin timMG<=8'b01011001;timCG<=8'b00011001;timY<=8'b00000011; end //89,25,3

else

begin

case(cs)

'b00:begin

if(timMG>0)

begin

begin if(timMG[3:0]==0) timMG<=timMG-7;

else timMG<=timMG-1;

end

tim<=timMG;

end

else begin tim<=0;timMG<=8'b01011001;

end

end

'b01:begin

if(timY>0)

begin

begin if(timY[3:0]==0) timY<=timY-7;

else timY<=timY-1;

end

tim<=timY;

end

else begin tim<=0;timY<=8'b00000011;

end

end

'b10:begin

if(timCG>0)

begin

begin if(timCG[3:0]==0) timCG<=timCG-7;

else timCG<=timCG-1;

end

tim<=timCG;

end

else begin tim<=0;timCG<=8'b00011001;

end

end

'b11:begin

if(timY>0)

begin

begin if(timY[3:0]==0) timY<=timY-7;

else timY<=timY-1;

end

tim<=timY;;

end

else begin tim<=0;timY<=8'b00000011;

end

end

default:begin

timMG<=8'b01011001;timCG<=8'b00011001;

timY<=8'b00000011;tim<=0;

end

endcase

end

//数码管显示

always@(posedge clk1)

begin

case(gw)

0:SG0<=7'b1000000; 1:SG0<=7'b1111001;

2:SG0<=7'b0100100; 3:SG0<=7'b0110000;

4:SG0<=7'b0011001; 5:SG0<=7'b0010010;

6:SG0<=7'b0000010; 7:SG0<=7'b1111000;

8:SG0<=7'b0000000; 9:SG0<=7'b0010000; //7段译码值

endcase

case(sw)

0:SG1<=7'b1000000; 1:SG1<=7'b1111001;

2:SG1<=7'b0100100; 3:SG1<=7'b0110000;

4:SG1<=7'b0011001; 5:SG1<=7'b0010010;

6:SG1<=7'b0000010; 7:SG1<=7'b1111000;

8:SG1<=7'b0000000; 9:SG1<=7'b0010000; //7段译码值

endcase

end

endmodule

(四)管脚分配

Input

Clk AF14 S AC12

Rst AB12

Output

MG,CR,MY,MR,CG,CY led9-led4

SG0,SG1; 数码管1-0文章来源地址https://www.toymoban.com/news/detail-433960.html

到了这里,关于EDA实验(Quartus Ⅱ+fpga) (四)---交通灯设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!