VHDL程序结构:

- 条件语句

if_then_else_end if - 数据类型

BIT类型(取逻辑位’1’或’0’)、整数类型INTEGER、布尔类型BOOLEAN(取TRUE或FALSE)、标准逻辑类型STD_LOGIC等 - 进程语句与顺序语句

process(敏感信号表)_endprocess

VHDL中所有的顺序语句都必须放在进程语句中 - 端口语句

port(端口模式;端口数据类型); - 端口模式

in:输入端口

out:输出端口

inout:双向端口

buffer:缓冲端口 - 关键字

(不区分大小写)entity、architecture、end、if、else、in、out等; - 标识符

(不区分大小写)自定义实体名、结构体名、端口名、信号名等;

- std_logic 数据类型九种含义

| 取值 | 含义 |

|---|---|

| ‘U’ | 未初始化 |

| ‘X’ | 强未知 |

| ‘0’ | 强逻辑0 |

| ‘1’ | 强逻辑1 |

| ‘Z’ | 高阻态 |

| ‘W’ | 弱未知 |

| ‘L’ | 弱逻辑0 |

| ‘H’ | 弱逻辑1 |

| ‘-’ | 忽略 |

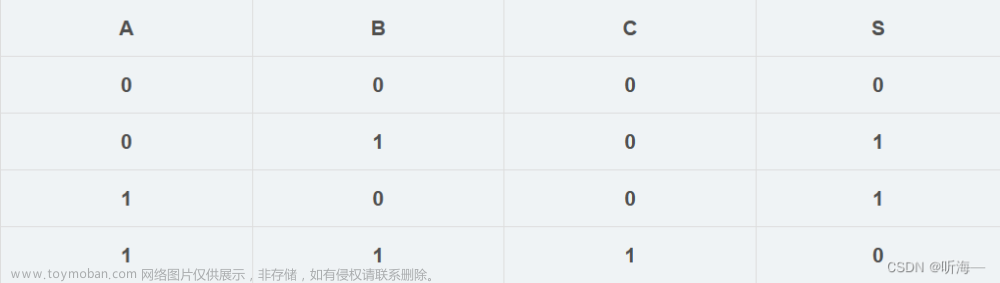

半加器

library ieee;--标注库STD、工作库WORK默认是打开的

use ieee.std_logic_1164.all;--定义了std_logic数据类型

entity h_adder is

port(

A:in std_logic;

B:in std_logic;

SO:out std_logic;

CO:out std_logic

);

end entity h_adder;

architecture fh1 of h_adder is

begin

SO <= A xor B;

CO <= A and B;

end architecture fh1;

多路选择器/case语句

library ieee;

use ieee.std_logic_1164.all;

entity MAX41A is

port(a,b,c,d,s0,s1:in std_logic; y:out std_logic);

end entity MAX41A;

architecture BHV of MAX41A is

signal s: std_logic_vector(1 downto 0);

begin

s <= s1 & s0;

process(s) begin --放s0,s1或直接放s

case (s) is

when "00" => y<=a;

when "01" => y<=b;

when "10" => y<=c;

when "11" => y<=d;

when others => null;

end case;

end process;

end BHV;

文章来源:https://www.toymoban.com/news/detail-433993.html

文章来源:https://www.toymoban.com/news/detail-433993.html

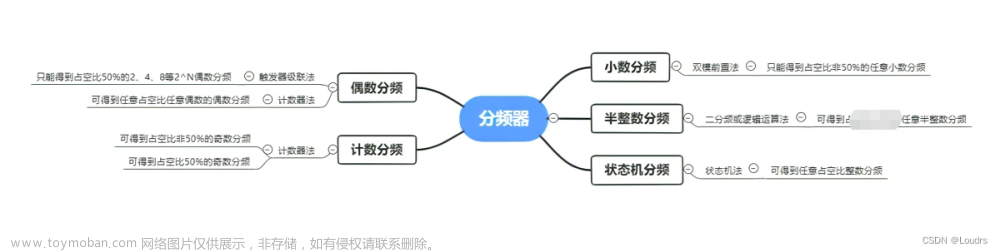

分频器

library ieee; ---表示打开IEEE库,因为IEEE库不属于VHDL的标准库,所以使用库的内容要先声明

use ieee.std_logic_1164.all;--定义std_logic/std_logic_vector

use ieee.std_logic_arith.all;-- 定义有无符号类型与对应运算

use ieee.std_logic_unsigned.all;-- 定义std_logic std_logic_vector

entity fenpingqi is -- entity只是定义所需的全部输入/输出信号

generic(

sys_clk_fre_value:INTEGER:=50000000;--系统时钟50MHz

div_clk_fre_value:INTEGER:=12500000--4分频

);

port(

i_sys_clk:in STD_LOGIC;--系统时钟

i_sys_rst:in STD_LOGIC;--系统复位

o_div_clk:out STD_LOGIC--系统输出

);

end entity fenpingqi;

architecture behavior of fenpingqi is

signal r_div_count:STD_logic_vector(31 downto 0);--32位的向量 2^32Hz > 50MHz(输入频率)

signal r_div_clk:STD_LOGIC;

begin

process(i_sys_clk,i_sys_rst)

begin

if(i_sys_rst='1')then--复位信号为高电平

r_div_count<=x"00000000";--分频计数置全0

r_div_clk<='0';--分频结果置0

elsif(i_sys_clk'event AND i_sys_clk='1')then

if(r_div_count=sys_clk_fre_value/div_clk_fre_value/2-1)then

r_div_count<=x"00000000";

r_div_clk<=NOT r_div_clk;

else

r_div_count <= r_div_count+1;--分频计数+1

end if;

end if;

end process;

o_div_clk<=r_div_clk;--输出

end architecture behavior;

Simulator:Quartus II Simulator. 文章来源地址https://www.toymoban.com/news/detail-433993.html

文章来源地址https://www.toymoban.com/news/detail-433993.html

到了这里,关于VHDL学习笔记——半加器 多路选择器 分频器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!