什么是锁相环技术?

用在接收机中,因为在相干解调的时候,需要接收机产生一个和发射机同频同相的载波频率,这时候就要对发射机处的载波频率进行精确的追踪,锁相环技术就是这样精准跟踪载波频率的一种技术。

锁相环(PLL)是一种数字信号处理技术,用于将输入的模拟信号转换成数字信号并进行处理。该技术常用于广播、雷达、音频、视频和通信等领域。

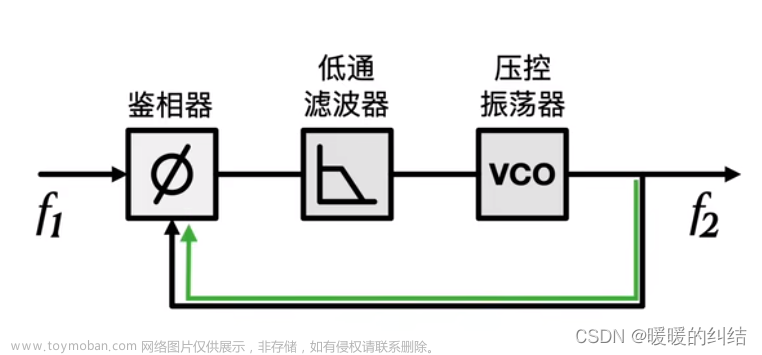

锁相环技术的原理是将输入的模拟信号进行采样,并将采样值与一个参考信号进行比较。通过比较,锁相环会产生一个误差信号,并根据该误差信号调整输入信号的相位和频率。最终,该技术可以将输入信号转换成数字信号,并进行处理。

锁相环技术的优点是精度高、抗噪声性强、可编程控制等。该技术可以将输入信号的相位和频率精确地控制,从而实现高质量的数字信号处理。此外,锁相环技术还可以进行自适应调整,以适应不同的信号和环境。

锁相环技术在广播、雷达、音频、视频和通信等领域得到了广泛的应用。例如,在广播领域,锁相环技术被用于稳定和跟踪载波信号;在雷达领域,锁相环技术被用于跟踪雷达目标的位置和速度;在音频和视频领域,锁相环技术被用于实现音频和视频的同步和去噪等。

总之,锁相环技术是一种非常重要的数字信号处理技术,具有广泛的应用前景。

怎么理解单边带信号?

单边带信号是一种数字信号,它只有一个频带,并且只有在需要的时候才进行数字解调。单边带信号的频带通常是固定的,例如在音频和视频通信中,每个符号只有一个频率通过。

在单边带信号中,数字信号只有在需要的时候才被解调。这通常是在接收端进行的,以便将接收到的数字信号转换回模拟信号。解调器的作用是将数字信号从频带上移除,并将其转换回模拟信号。

与调制相比,单边带信号具有更高的传输效率和更低的误码率。由于它只在需要时进行数字解调,因此它可以减少信号传输时的能量消耗,并且在接收端更容易进行解调。

总之,单边带信号是一种相对简单但高效的数字信号处理方法,它可以提高信号的传输速率和效率,并且在接收端更容易进行解调。

为什么要对信号进行调制?

对信号进行调制是将模拟信号转换成数字信号的过程。调制是一种将模拟信号转换成数字信号的方法,它可以提高信号的传输速率和效率。调制通常包括将模拟信号转换成数字信号和将数字信号转换回模拟信号两个过程。

在调制过程中,需要使用调制器将模拟信号转换成数字信号,并将数字信号加载到一个频带上。调制器可以是模拟的,也可以是数字的。数字调制器具有更高的抗噪声性能和更好的频带利用率,因此在现代通信系统中被广泛使用。

调制后的数字信号需要解调器进行解调,以将其转换回模拟信号。解调器的作用是将数字信号从频带上移除,并将其转换回模拟信号。解调器可以是数字的,也可以是模拟的。文章来源:https://www.toymoban.com/news/detail-434637.html

对信号进行调制可以提高信号的传输速率和效率,因为数字信号比模拟信号更容易传输和处理。此外,调制技术还可以提供更好的抗噪声性能和更高的频带利用率,从而实现更好的通信质量。文章来源地址https://www.toymoban.com/news/detail-434637.html

到了这里,关于锁相环技术,单边带信号,信号的调制的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!