前言

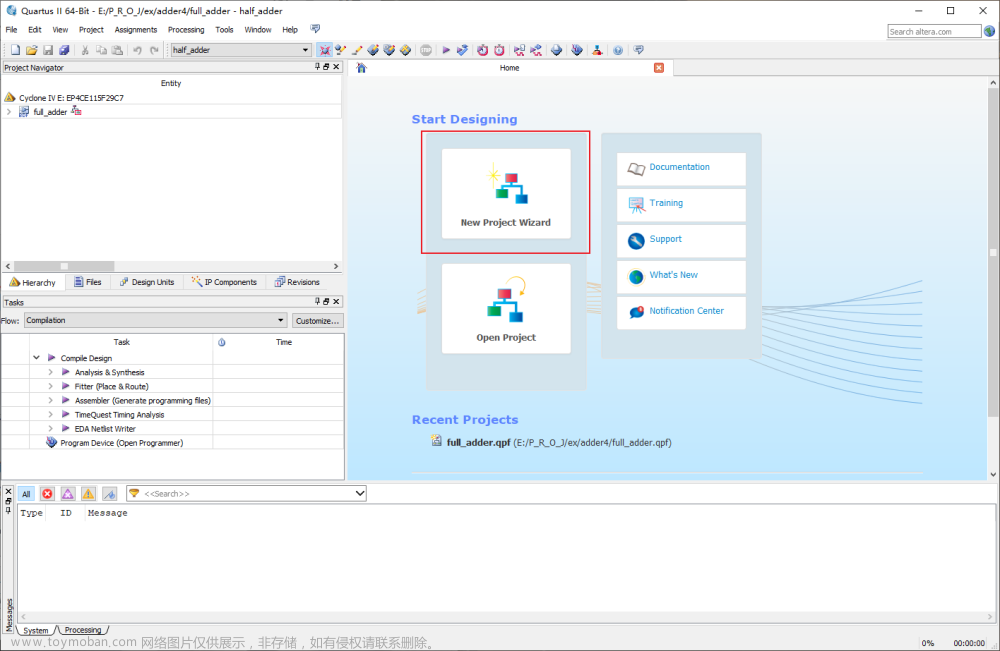

本文主要介绍了Quartus II 9.1web 免安装版的一个入门使用案例和常见问题的解决方法。

使用步骤

一:创建工程和bdf文件

首先打开Quartus II,选择File->New

然后在New界面下选择Block Diagram/Schematic File,这时会出现一张空白原理图。

选择左侧的symbol tool,然后按照下图框中的路径找到not(非门),点击ok放置到原理图中,本文以简单的非门为例。

摆放完非门后加入输入管脚和输出管脚,还是在刚才symbol tool 下找到pin文件夹选择input_pin和output_pin。

点击ok进行摆放得到下图

将光标移动至管脚附近待光标呈下方形状后可将两端口进行连接。

连接完成后得到下图

ctrl+s进行保存,保存后会出现工程创建向导

点击next配置工作路径和项目文件

选择刚才创建的.bdf文件

下两页保持默认,点击next。

最后一页点击Finish完成创建。

点击上方选项卡的向右指的紫色三角箭头进行编译

完成编译后的界面

二:创建波形仿真文件

新建一个vector waveform file

此时还没有添加节点,在name下方空白区域右键进行插入节点

点击node_finder

文章来源地址https://www.toymoban.com/news/detail-434733.html

按下图顺序进行点击

先将pin_name加入到右侧已选择的节点

点击ok后可以看到输入节点INPUT已近成功加入

同理将输出节点OUTPUT也进行加入

完成后可以发现Name下面有两个节点

点击输入节点pin_name对其进行波形的配置,这里选择的是clock

按照下图进行配置参数,图中参数仅是示例可以自己灵活配置

点击ok后得到以下输入波形(如果没有显示的话就按住ctrl滚动鼠标滚轮进行放大或者缩小)

ctrl+s保存waveform1文件

点击下方箭头进行仿真

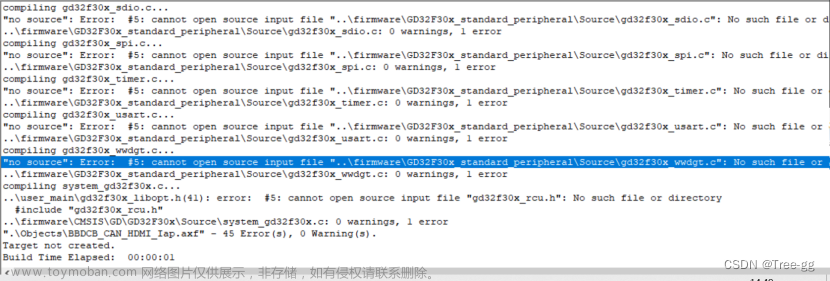

此时出现错误没有分配仿真的输入文件,点击Assignments->Settings进行配置

成功添加刚才保存的.vwf文件后点击ok

这时OUTPUT节点就出现了与INPUT相反的波形,但有一些延迟。这时因为本例只是一个简单的组合逻辑门电路不是时序逻辑电路,回到刚才最后添加.vwf文件的界面下将Simulation mode从Timing改为Functional。

然后在Processing中点击产生Funtional Simulational Netlist

模式改变后,回到之前的.vwf文件重新进行仿真

重新仿真后波形恢复正常

文章来源:https://www.toymoban.com/news/detail-434733.html

文章来源:https://www.toymoban.com/news/detail-434733.html

总结

以上就是本文要讲的全部内容,本文只简单介绍了Quartus II的使用,方便新手进行入门。

到了这里,关于Quartus II简单仿真及no simulation input file错误解决方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!