一般的集成电路芯片从设计到出货上板,基本流程可分为 电路设计→晶圆制造→晶圆测试→IC封装→封装后测试→出货,那么我们主要做的工作就是封装后测试。

这里的IC测试主要有两个目的:1、确认被测芯片是否符合手册上定义的规范 2、通过测试确定芯片正常工作的边界条件。根据芯片制造商提供的待测DUT的spac,来完成相关的测试代码开发,最终生成一个自动化测试的OI,那么工厂在量产测试的时候就可对每一个芯片自动化进行测试,之后会生成一份测试报告,可直观的看出该批芯片的合格率与不合格率,以及不合格项是什么。

对于集成电路测试来说可分为特性化分析、量产测试以及老化测试。

特性化分析一般是在芯片设计阶段进行的,是为了确定产品规格,明确产品正常工作的条件进行的,可使用仪器仪表进行,也可以接住自动化测试设备ATE实现。比如借助ATE设备进行扫描测试的时候,NI的Digital Pattern Editor工具就提供了shmoo图的功能,可以实现对两个变化的参数的扫描,以确定产品工作的边界条件。

量产测试是为了避免单颗IC芯片不良导致的缺陷,因此要对批量生产的每一颗IC进行测试,这里包括两种测试,分别是芯片探针测试(Chip Pobing,CP)和最终成品测试(Final Test,FT)。CP测试针对的是为切割的晶圆,需要用探针接触晶圆上的测试焊盘,一次可测晶圆上的单个或多个晶粒(Die);FT测试则针对已经封装好的IC成品,用弹簧针连接IC外引脚测试。ATE针对这两种测试使用不同的机械手,CP测试使用探针台(Prober),FT测试使用分选机(Handler)。

老化测试是为了预测产品的使用寿命,提出早期失效的产品。老化测试一般是把产品放在恒温箱里,通过恒温或温度循环对产品进行测试。

CP测试流程:晶圆库→晶圆质量检验→晶圆测试→烘烤→晶圆检查→包装&质检&出货

CP流程一般可理解为CP1测试基本的存储读写功能,并在存储芯片内写入一定的内容;然后晶圆经过高温烘烤后进行CP2测试,检验之前写入的数据是否可以保持;最后对MCU部分进行逻辑功能的CP3测试。

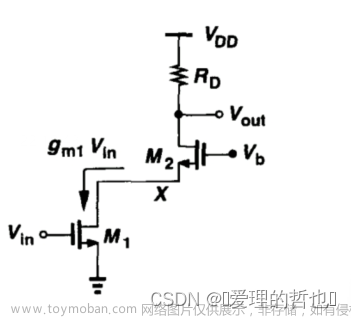

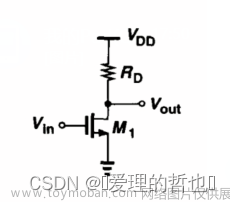

CP测试系统包括ATE(测试机头、测试机头支架、工作站)、针测接口板(PIB)、针塔、探针卡、晶圆卡盘、探针台,CP测试系统示意图如下图。

测试程序一般保存在工作站中,在工作站上打开操作界面(Operation Interface,OI)控制程序加载,开始,停止,记录和存储测试结果,以及实时显示测试进度和状态。测试完成后,保存数据、结果统计和晶圆测试结果图。

探针台通过连接ATE的通信接口接收ATE发来的开始指令,调整探针正确接触某一颗晶粒的测试焊盘,然后发送反馈信号给ATE并开始测试。ATE测试完成后把测试结果记录到Datalog文件,并向探针台反馈测试分类(Bin)的结果。

探针卡是连接ATE与晶圆上被测电路的重要接口。

FT测试流程有两种,分别是分体式分选机(使用大尺寸IC)和一体式分选机(适用小尺寸IC,<3mm*3mm)

FT测试系统包括ATE(测试机头、测试机头支架、工作站)、分选机、和测试配件(Load Board、Socket、模具Kit),FT测试系统示意图如下图。

FT测试流程:

1)架机。在测试机上安装负载板、Socket和连接板,然后用螺钉将连接板固定在分选机测试区,并将测试模具中其他配件安装在分选机上,调试好吸放料感应位置,再接上通信接口。

2)架机完成后,在测试机上加载出测试程序。

3)在分选机上按开始按钮,分选机将待测芯片放至测试区,准备好后反馈开始测试给测试机。

4)测试机收到开始信号后开始测试,测试完成发送测试结束信号和分Bin结果给分选机。

5)分选机接收Bin信号,把测试完成的芯片放置到预先设定好的分Bin料盘。

6)移动未测试料到测试区,开始下一轮测试。

7)重复步骤至所有物料完成,操作界面提示测试技术,生成测试数据。

文章来源地址https://www.toymoban.com/news/detail-434872.html文章来源:https://www.toymoban.com/news/detail-434872.html

到了这里,关于集成电路测试简介(1)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!