文章来源地址https://www.toymoban.com/news/detail-435097.html

文章目录

目录

文章目录

实验一:Logisim软件的使用

实验二:数据的表示

1.汉字的编码实验:

实验三:运算器组成实验

1.多位串行加法器和多位可控加减电路的设计

2.快速加法器的设计

3.多位算术逻辑单元ALU设计

4.阵列乘法器设计

4.阵列除法器设计

实验四:存储系统综合实验

1.存储扩展实验

2.MIPS RAM 设计

3.Cache设计实验

实验五: MISP程序设计实验

1.创建并运行一个MIPS汇编程序在MARS环境下创建HelloWorld.asm文件,然后汇编运行该汇编程序。

2.算术运算实验

3.分支结构实验

4.循环结构实验

5.数组实验

6.数组排序实验

文章来源:https://www.toymoban.com/news/detail-435097.html

实验一:Logisim软件的使用

任务1:在logisim的管理窗口创建名为“2-4 Decode”的子电路完成2-4译码器电路图的绘制,并分别用自动仿真、和单步仿真验证其逻辑功能。

实验结果图:

任务2:在logisim的管理窗口创建名为“2:1MUX”的二路选择器的子电路,应用该子电路创建完成一名为“4:1MUX”的四路选择器的子电路。

实验结果图:

实验结果图:

任务3:在logisim的管理窗口创建名为“SUM”的子电路,利用logisim“project”中的“Analyze Circuit ”实现自动生成下列表达式的逻辑电路图。并查看其对应的真值表。逻辑表达式如下:

S= a xor b +b xor c +a xor c

carry=a & b +b & c +c & a

实验结果图:

任务4:在logisim的管理窗口创建名为“Write-RAM”的子电路,完成下图的绘制,利用logisim“Simulate”中的“Ticks Enabled”在RAM中的所有单元写入数据。

实验结果图:

实验二:数据的表示

1.汉字的编码实验:

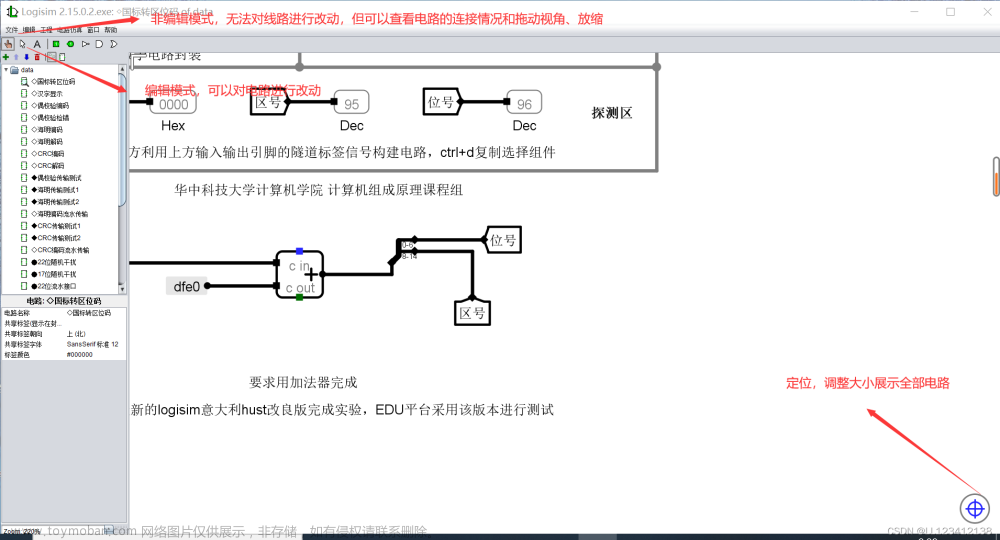

(1)设计GB2312码转区位码电路

在logisim中打开“数据表示实验2.circ”文件,在对应电路中完成GB2312码转区位码的子电路的设计。

(2)汉字GB2312编码实验

完成GB2312编码转换子电路的设计后,在汉字显示电路中进行测试。

实验结果图:

国标转区位码:

偶校验编码:

偶校验检错:

实验三:运算器组成实验

1.多位串行加法器和多位可控加减电路的设计

(1)在logisim中打开“运算器实验3.circ”文件,在对应电路中完成8位串行加法器电路的设计。 并仿真验证设计的正确性。

(2)在打开的“运算器实验3.circ”文件中找到“☆8位可控加减法器”子电路,完成8位可控加减法器的设计。并仿真验证设计的正确性。、

实验结果图:

(1)八位串行加法器

(2)8位可控加减法器

2.快速加法器的设计

- 利用相关知识设计4位先行进位电路。

- 利用设计的4位先行电路构造4位快速加法器。

- 利用4位快速加法器构造16位的快速加法器。

- 再利用16位的快速加法器构造32位的快速加法器。

实验结果图:

(1)4位先行进位电路

(2)4位快速加法器

(3)16位的快速加法器

(4)32位的快速加法器

3.多位算术逻辑单元ALU设计

- 利用自己设计的32位快速加法器和Logisim中的组件设计完成指定规格的32位ALU单元。

- 利用“ALU自动测试”电路测试ALU各种运算功能的正确性。

实验结果图:

4.阵列乘法器设计

-

利用已经设计完成的“5位乘法与门阵列电路”,设计完成不带符号的5位阵列乘法器。并仿真验证设计的正确性。

实验结果图:

不带符号的五位阵列乘法器:

4.阵列除法器设计

1.完成一位可控加减单元的电路设计。

2.利用一位可控加减单元完成不恢复余数的4位阵列除法器。并仿真验证设计的正确性。

实验结果图:

一位可控加减单元的电路设计:

不恢复余数的4位阵列除法器:

实验四:存储系统综合实验

1.存储扩展实验

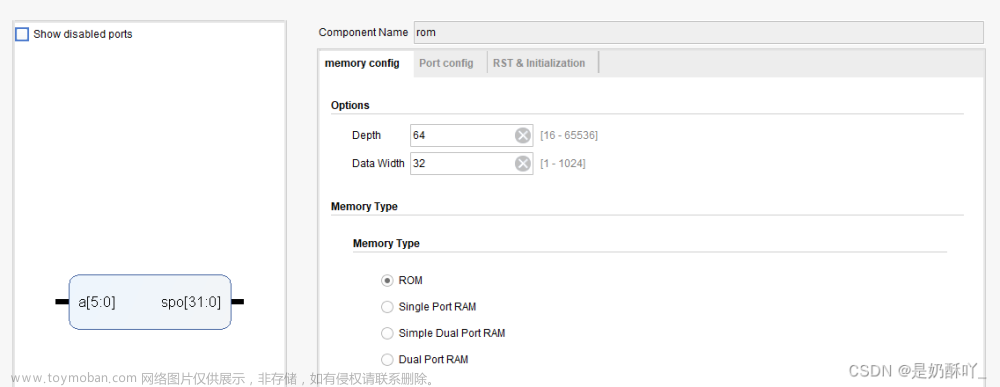

- 设计完成字库电路:在打开的“存储器实验4.circ”文件中找到“☆字库电路”子电路,利用给定的4 个 4K*32 位 ROM,7 个 16K*32 位 ROM,请构建 GB2312 16*16 点阵字库存储器电路, 电路输入为汉字区号和位号。本实验的主要目的是进行存储器字扩展(容量扩展, 地址总线扩展),实验工程文件中已经提供了一个参考实现“参考字库”子电路, 完成实验所需的点阵信息均可以通过该子电路直接导出后载入, 也可直接复制拷贝。

- 对完成的字库电路进行功能测试:利用“存储器实验4.circ”文件中“★字库测试”子电路对完成的字库电路进行功能测试。 通过对比上下两个显示区显示内容是否一致即可验证字库功能正确性。

实验结果图:

(1)字库电路:

(2)字库测试:

2.MIPS RAM 设计

- 设计完成MIPS RAM

- 对设计完成的 MIPS RAM 电路进行功能测试

实验结果图:

(1)MIPS RAM

(2)MIPS RAM测试

3.Cache设计实验

实验结果图:

直接相联

实验五: MISP程序设计实验

1.创建并运行一个MIPS汇编程序在MARS环境下创建HelloWorld.asm文件,然后汇编运行该汇编程序。

代码:

#HelloWorld.asm

.data #数据段开始

OutString: .asciiz "Hello world!\n"

.text #代码段开始

main:

li $v0, 4 #4号系统调用,打印字符串

la $a0, OutString

syscall

li $v0, 10 #10号系统调用,程序退出

syscall实验结果图:

2.算术运算实验

编写MIPS汇编程序AddSub.asm,完成如下C语言代码相同的功能。要求变量A-F存储在暂存寄存器中,结果Z存储在内存中并输出。

//AddSub.c

int main()

{

int A=15;

int B=10;

int C=7;

int D=2;

int E=18;

int F=-3;

int Z=0;

Z=(A+B)+(C-D)+(E+F)-(A-C);

Printf(“%d”,Z);

}

代码:

.data

var0: .word 0

var1 : .word 15

var2: .word 10

var3: .word 7

var4: .word 2

var5: .word 18

var6: .word -3

.text

main:

lw $t0,var0

lw $t1,var1

lw $t2,var2

lw $t3,var3

lw $t4,var4

lw $t5,var5

lw $t6,var6

add $t0,$t1,$t2

sub $t2,$t3,$t4

add $t4,$t5,$t6

sub $t5,$t1,$t3

add $t6,$t0,$t2

add $t3,$t6,$t4

sub $t0,$t3,$t5

sw $t0,var0

lw $t0,var0

li $v0,1

move $a0,$t0

syscall实验结果图:

3.分支结构实验

编写MIPS汇编程序Branch.arm,完成如下C语言代码相同的功能,要求A、B、C和Z必须是内存中的整型变量,程序运行过程中可以加载到寄存器,每次运行之前可以修改A、B、C的初始值,可以使用MIPS中与分支相关的伪指令使得比较和分支代码更简单。

C语言代码如下:

//Branch.c

int main( )

{

if(A>B || C<5)

Z=1;

else if(A==B)

Z=2;

else

Z=3;

switch(Z)

{case 1:

Z=-1;

break;

case 2:

Z=-2;

break;

default:

Z=0;

break;}

}代码:

.data

A: .word 1

B: .word 2

C: .word 3

Z: .word

.text

main:

lw $t2,A

lw $t3,B

lw $t4,C

li $t5,5

bgt $t2,$t3,s1

bgt $t5,$t4,s1

beq $t2,$t3,s2

j s3

s1:

li $t1,1

sw $t1,Z

li $v0,1

j ju

s2:

li $t1,2

sw $t1,Z

li $v0,1

j ju

s3:

li $t1,3

sw $t1,Z

li $v0,1

j ju

ju:

li $t2,1

li $t3,2

lw $t4,Z

beq $t2,$t4,z1

beq $t3,$t4,z2

j z3

z1:

li $t1,-1

sw $t1,Z

li $v0,1

j re

z2:

li $t1,-2

sw $t1,Z

li $v0,1

j re

z3:

li $t1,0

sw $t1,Z

li $v0,1

j re

re:

li $v0,1

lw $a0,Z

syscall

li $v0, 10 #10号系统调用,程序退出

syscall实验结果图:

4.循环结构实验

编写MIPS汇编程序Loop.arm,完成如下C语言代码相同的功能,要求i和Z必须是内存中的整型变量,程序运行过程中可以加载到寄存器,每次运行之前可以修改i和Z的初始值,可以使用MIPS中与分支相关的伪指令使得比较和分支代码更简单。

C语言代码如下:

//Branch.c

int main( )

{

int Z=2;

int i=40;

Do{

Z++;

}while(Z<100);

while(i>0)

{Z--;

-;}

Printf(“%d,%d”,Z,i);

}代码:

.data

i: .word 40

Z: .word 2

c: .asciiz ","

.text

main:

lw $t0,Z

lw $t1,i

loop:

add $t0,$t0,1

blt $t0,100,loop

loop2:

bgtz $t1,tt

j print

tt:

sub $t0,$t0,1

sub $t1,$t1,1

j loop2

print:

sw $t0,Z

sw $t1,i

li $v0,1

lw $a0,Z

syscall

li $v0, 4 #4号系统调用,打印字符串

la $a0, c

syscall

li $v0,1

lw $a0,i

syscall

li $v0, 10 #10号系统调用,程序退出

syscall

实验结果图:

5.数组实验

编写MIPS汇编程序array.arm,完成如下C语言代码相同的功能,要求A和B必须是内存中的整型数组,C是内存整型变量,i可以是寄存器。

//array.c

int main( )

{

int A[6];

int B[6]={1,2,3,4,5,6};

int C=10;

int i;

for(i=0;i<6;,i++)

{ A[i]=B[i]+C;}

}代码:

.data

A: .space 24

B: .word 1,2,3,4,5,6

C: .word 10

i: .word

c: .asciiz ","

.text

main:

li $t0,0

loop:

lw $t1,B($t0)

add $t2,$t1,10

sw $t2,A($t0)

add $t0,$t0,4

blt $t0,24,loop

li $t0,0

loop2 :

li $v0,1

lw $a0,A($t0)

syscall

li $v0, 4 #4号系统调用,打印字符串

la $a0, c

syscall

add $t0,$t0,4

blt $t0,24,loop2

li $v0, 10 #10号系统调用,程序退出

syscall实验结果图:

6.数组排序实验

编写MIPS汇编程序ArraySort.arm,完成如下C语言代码相同的功能,要求a必须是内存中的整型数组,必须使用MIPS过程调用机制实现对应C函数,建议用十进制显示数据和寄存器的值,以便观察结果。

int swap(int *x, int *y)

{ if(*x>*y)

{int t=*x;*x=*y;*y=t;

return 1;

}

return 0;

}

int main()

{ int a[10]={10,20,50,-2,8,-8,34,-35,80,-19};

int i,j,n=0;

for(i=0;i<9;i++)

{for(j=i+1;j<10;j++)

n+=swap(&a[i],&a[j]);

}

printf(“%d”,n);

}代码:

.data

a: .word 10,20,50,-2,8,-8,34,-35,80,-19

i: .word

j: .word

n: .word 0

.text

main:

li $t0,0

lw $t2,n

loop1:

add $t1,$t0,4

blt $t0,36,loop2

li $t0,0

j print

loop2:

blt $t1,40,swap

add $t0,$t0,4

j loop1

swap:

lw $t3,a($t0)

lw $t4,a($t1)

ble $t3,$t4,ju

sw $t4,a($t0)

sw $t3,a($t1)

add $t2,$t2,1

ju:

add $t1,$t1,4

j loop2

print:

sw $t2,n

li $v0,1

lw $a0,n

syscall

li $v0, 10 #10号系统调用,程序退出

syscall实验结果图:

到了这里,关于计算机组成原理实验(logisim)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!