最近在仿真sdram,遇到了一些问题,现在解决了,写出来分享给大家。

问题:

使用quartus和modelsim联合仿真sdram的时候,tb文件中例化了sdram的top文件和sdram的仿真模型,这样会报错,我就想着直接在modelsim中仿真,但是由于模块中有quartus生成的ip核,只在modelsim中仿真也会报错,我就在想,怎么才能把ip核拿来放在modelsim中,搜了一天终于搞出来了,心累。。。。文章来源:https://www.toymoban.com/news/detail-435470.html

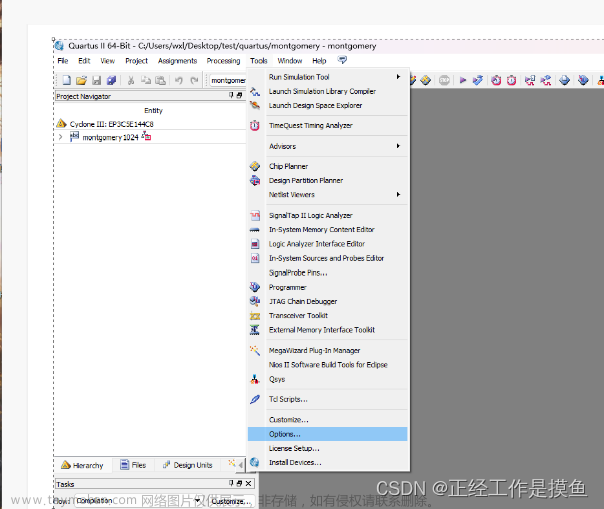

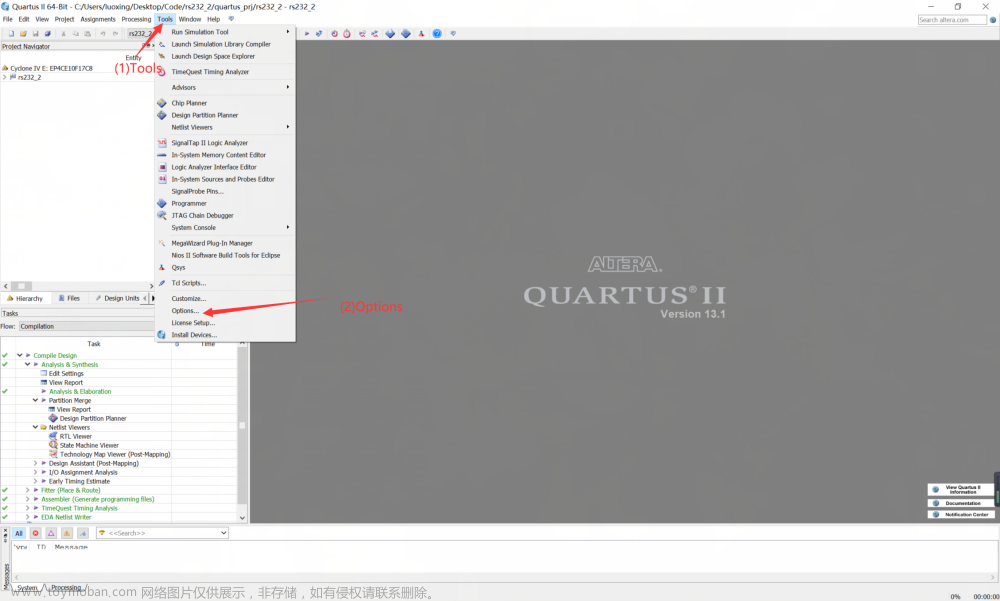

首先,需要altera中所有ip核编译到的modelsim的library中,这里贴出链接,我就只按照这个来的,大家仿照就行了,如何用ModelsimSE仿真IP核-以PLL为例 - 百度文库 (baidu.com)文章来源地址https://www.toymoban.com/news/detail-435470.html

首先,需要altera中所有ip核编译到的modelsim的library中,这里贴出链接,我就只按照这个来的,大家仿照就行了,如何用ModelsimSE仿真IP核-以PLL为例 - 百度文库 (baidu.com)文章来源地址https://www.toymoban.com/news/detail-435470.html

到了这里,关于如何用modelsim仿真包含quartus IP核的工程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!