备注:本次设计以XCZU28DR-2FFVG1517E为例,其他系列的电源设计类似。

1 简介

赛灵思 Zynq® UltraScale+™ RFSoC 支持 -2 和 -1 速度等级,其中 -2E 器件性能最高。-2LE 和 -1LI 器件可以 0.85V 或 0.72V 的 VCCINT 电

压工作,专为实现更低的最大静态功耗而设计。使用以 VCCINT = 0.85V 工作的 -2LE 和 -1LI 器件时,L 器件的速度规格与 -2I 或 -1I 速度

等级相同。以 VCCINT = 0.72V 工作时,-2LE 和 -1LI 器件的性能以及静态和动态功耗都将下降。

DC 和 AC 特性按以下温度范围来指定:扩展级 (E)、工业级 (I) 和军工级 (M)。除正常工作的温度外或者除非另行说明,否则特定速度等级

的所有 DC 和 AC 电气参数都相同(即,-1 速度等级的扩展级器件的时序特性与 -1 速度等级的工业级器件相同)。但在每个温度范围

内,仅限选定的速度等级和/或器件才可用。

本数据手册中的 XQ 参考信息仅适用于 XQ 加固型封装中可用的器件。请参阅《军用级 UltraScale 架构数据手册:简介》 (DS895),以获

取有关 XQ 军用级器件编号、封装和订购的更多信息。

所有供电电压和结温规格均代表最差情况下的规格。所含参数为常用设计和典型应用的公用参数。

1 绝对最大额定值

1.1 处理器系统 (PS)

| 标识 | 描述 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| VCC_PSINTFP | PS 主逻辑全功耗域供电电压 | -0.500 | 1.000 | V |

| VCC_PSINTLP | PS 主逻辑低功耗域供电电压 | -0.500 | 1.000 | V |

| VCC_PSAUX | PS 辅助供电电压 | -0.500 | 2.000 | V |

| VCC_PSINTFP_DDR | PS DDR 控制器和 PHY 供电电压 | -0.500 | 1.000 | V |

| VCC_PSADC | GND_PSADC 相关的 PS SYSMON ADC 供电电压 | -0.500 | 2.000 | V |

| VCC_PSPLL | PS PLL 供电电压 | -0.500 | 1.320 | V |

| VPS_MGTRAVCC | PS-GTR 供电电压 | -0.500 | 1.000 | V |

| VPS_MGTRAVTT | PS-GTR 终端电压 | -0.500 | 2.000 | V |

| VPS_MGTREFCLK | PS-GTR 参考时钟输入电压 | -0.500 | 1.100 | V |

| VPS_MGTRIN | PS-GTR 接收器输入电压 | -0.500 | 1.100 | V |

| VCCO_PSDDR | PS DDR I/O 供电电压 | -0.500 | 1.650 | V |

| VCC_PSDDR_PLL | PS DDR PLL 供电电压 | -0.500 | 2.000 | V |

| VCCO_PSIO | PS I/O 供电电压 | -0.500 | 3.630 | V |

| VPSIN | PS I/O 输入电压 | -0.500 | VCCO_PSIO + 0.550 | V |

| VPSIN | PS DDR I/O 输入电压 | -0.500 | VCCO_PSDDR + 0.550 | V |

| VCC_PSBATT | PS 电池供电式 RAM 和电池供电式实时时钟 (RTC) 供电电压 | -0.500 | 2.000 | V |

1.2 可编程逻辑(PL)

| 标识 | 描述 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| VCCINT | 内部供电电压 | -0.500 | 1.000 | V |

| VCCINT_IO | I/O bank 的内部供电电压 | -0.500 | 1.000 | V |

| VCCAUX | 辅助供电电压 | -0.500 | 2.000 | V |

| VCCBRAM | 块 RAM 存储器的供电电压 | -0.500 | 1.000 | V |

| VCCO | HD I/O bank 的输出驱动供电电压 | -0.500 | 3.400 | V |

| VCCO | HP I/O bank 的输出驱动供电电压 | -0.500 | 2.000 | V |

| VCCAUX_IO | I/O bank 的辅助供电电压 | -0.500 | 2.000 | V |

| VREF | 输入参考电压 | -0.500 | 2.000 | V |

| VIN | HD I/O bank 的 I/O 输入电压 | -0.550 | VCCO + 0.550 | V |

| VIN | HP I/O bank 的 I/O 输入电压 | -0.550 | VCCO + 0.550 | V |

| IDC | 焊盘可用输出电流 | -20 | 20 | mA |

| IRMS | 焊盘可用 RMS 输出电流 | -20 | 20 | mA |

1.3 GTY收发器

| 标识 | 描述 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| VMGTAVCC | 收发器电路的模拟供电电压 | -0.500 | 1.000 | V |

| VMGTAVTT | 收发器终端电路的模拟供电电压 | -0.500 | 1.300 | V |

| VMGTVCCAUX | 收发器的辅助模拟四通道 PLL (QPLL) 供电电压 | -0.500 | 1.900 | V |

| VMGTREFCLK | 收发器参考时钟绝对输入电压 | -0.500 | 1.300 | V |

| VMGTAVTTRCAL | 收发器列的电阻校准电路的模拟供电电压 | -0.500 | 1.300 | V |

| VIN | 接收器 (RXP/RXN) 和发射器 (TXP/TXN) 绝对输入电压 | 0.500 | 1.200 | V |

| IDCIN-FLOAT | 接收器输入引脚 DC 耦合 RX 终端的 DC 输入电流 = 浮动 | N.A | 10 | mA |

| IDCIN-MGTAVTT | 接收器输入引脚 DC 耦合 RX 终端的 DC 输入电流 = VMGTAVTT | N.A | 10 | mA |

| IDCIN-GND | 接收器输入引脚 DC 耦合 RX 终端的 DC 输入电流 = GND | N.A | N.A | mA |

| IDCIN-PROG | 接收器输入引脚 DC 耦合 RX 终端的 DC 输入电流 = 可编程 | N.A | N.A | mA |

| IDCOUT-FLOAT | 发射器引脚 DC 耦合 RX 终端的 DC 输出电流 = 浮动 | N.A | 6 | mA |

| IDCOUT-MGTAVTT | 发射器引脚 DC 耦合 RX 终端的 DC 输出电流 = VMGTAVTT | N.A | 6 | mA |

- VCCINT_IO 必须连接到 VCCBRAM。

- VCCAUX_IO 必须连接到 VCCAUX。

- 针对 RX 终端 = 浮动,不支持 AC 耦合操作。

- 对于 GTY 收发器,针对 RX 终端 = GND,不支持 DC 耦合操作。

- 针对 RX 终端 = 可编程,不支持 DC 耦合操作。

2 推荐工作电压

2.1 处理器系统

| 标识 | 描述 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| VCC_PSINTFP | PS 全功耗域供电电压 | 0.808 | 0.850 | 0.892 | V |

| VCC_PSINTFP | 对于 -1LI、-2LI 和 -2LE (VCCINT = 0.72V) 器件:PS 全功耗域供电电压 | 0.808 | 0.850 | 0.892 | V |

| VCC_PSINTLP | PS 低功耗域供电电压 | 0.808 | 0.850 | 0.892 | V |

| VCC_PSINTLP | 对于 -1LI、-2LI 和 -2LE (VCCINT = 0.72V) 器件:PS 低功耗域供电电压 | 0.808 | 0.850 | 0.892 | V |

| VCC_PSAUX | PS 辅助供电电压 | 1.710 | 1.800 | 1.890 | V |

| VCC_PSINTFP_DDR | PS DDR 控制器和 PHY 供电电压 | -0.500 | 1.000 | V | |

| VCC_PSINTFP_DDR | 对于 -1LI、-2LI 和 -2LE (VCCINT = 0.72V) 器件:PS DDR 控制器和PHY 供电电压 | -0.500 | 1.000 | V | |

| VCC_PSADC | GND_PSADC 相关的 PS SYSMON ADC 供电电压 | 1.710 | 1.800 | 1.890 | V |

| VCC_PSPLL | PS PLL 供电电压 | 1.164 | 1.200 | 1.236 | V |

| VPS_MGTRAVCC | PS-GTR 供电电压 | 0.825 | 0.850 | 0.875 | V |

| VPS_MGTRAVTT | PS-GTR 终端电压 | 1.746 | 1.800 | 1.854 | V |

| VCCO_PSDDR | PS DDR I/O 供电电压 | 1.06 | N.A | 1.575 | V |

| VCC_PSDDR_PLL | PS DDR PLL 供电电压 | 1.710 | 1.800 | 1.890 | V |

| VCCO_PSIO | PS I/O 供电电压 | 1.710 | N.A | 3.465 | V |

| VPSIN | PS I/O 输入电压 | -0.200 | N.A | VCCO_PSIO + 0.200 | V |

| VPSIN | PS DDR I/O 输入电压 | -0.200 | N.A | VCCO_PSDDR + 0.200 | V |

| VCC_PSBATT | PS 电池供电式 RAM 和电池供电式实时时钟 (RTC) 供电电压 | 1.200 | N.A | 1.500 | V |

2.2 可编程逻辑

| 标识 | 描述 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| VCCINT | PL 内部供电电压 | 0.825 | 0.850 | 0.876 | V |

| VCCINT | 对于 -1LI、-2LI 和 -2LE (VCCINT = 0.72V) 器件:PL 内部供电电压 | 0.698 | 0.720 | 0.742 | V |

| VCCINT_IO | I/O bank 的 PL 内部供电电压 | 0.825 | 0.850 | 0.876 | V |

| VCCINT_IO | 对于 -1LI、-2LI 和 -2LE (VCCINT = 0.72V) 器件:I/O bank 的 PL 内部供电电压 | 0.825 | 0.850 | 0.876 | V |

| VCCBRAM | 块 RAM 存储器的供电电压 | 0.825 | 0.850 | 0.876 | V |

| VCCAUX | 辅助供电电压 | 0.825 | 0.850 | 0.876 | V |

| VCCO | HD I/O bank 的输出驱动供电电压 | 1.140 | N.A | 3.400 | V |

| VCCO | HP I/O bank 的输出驱动供电电压 | 0.950 | N.A | 1.900 | V |

| VCCAUX_IO | 辅助 I/O 供电电压 | 1.746 | 1.800 | 1.854 | V |

| VIN | I/O 输入电压 | -0.200 | N.A | VCCO + 0.200 | V |

| IIN | 对钳位二极管进行正向偏置时,流经已上电 bank 或未上电 bank 中的任意 PL 引脚或 PS 引脚的最大电流 | N.A | N.A | 10 | mA |

2.3 GTY收发器

| 标识 | 描述 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| VMGTAVCC | GTY 收发器的模拟供电电压 | 0.873 | 0.900 | 0.927 | V |

| VMGTAVTT | GTY 发射器和接收器终端电路的模拟供电电压 | 1.164 | 1.200 | 1.236 | V |

| VMGTVCCAUX | 收发器的辅助模拟 QPLL 供电电压 | 1.746 | 1.800 | 1.854 | V |

| VMGTAVTTRCAL1 | GTY 收发器列的电阻校准电路的模拟供电电压 | 1.164 | 1.200 | 1.236 | V |

- 所有电压都与 GND 相关。

- 如需了解配电系统的设计,请参阅《UltraScale 架构 PCB 设计用户指南》 (UG583)。

- VCC_PSINTFP_DDR 必须绑定到 VCC_PSINTFP。

- 列出的每项电压都必须按《UltraScale 架构 PCB 设计用户指南》 (UG583) 中所述进行滤波。

- VCCO_PSDDR 值包括 1.2V、1.35V、1.5V (±5%) 和 1.1V +0.07V/-0.04V,取决于特定存储器标准所需的容限。

- 适用于所有 PS I/O 供电 bank。VCCO_PSIO 值包括 1.8V、2.5V 和 3.3V (±5%)。

- 如果不使用电池供电式 RAM 或 RTC,请将 VCC_PSBATT 连接到 GND 或 VCC_PSAUX。在未使用的 VCC_PSBATT 上可接受 VCC_PSAUX 最大值 1.89V。

- VCCINT_IO 必须连接到 VCCBRAM。

- VCCO 值包括 1.0V(仅限 HP I/O)、1.2V、1.35V、1.5V1.8V、2.5V(仅限 HD I/O)(±5%) 和 3.3V(仅限 HD I/O)(+3/–5%)。

- VCCAUX_IO 必须连接到 VCCAUX。

- 始终适用较低的绝对电压规格。

- 每个 bank 不得超过总计 200 mA。

- 列出的每项电压都必须按《UltraScale 架构 GTY 收发器用户指南》 (UG578) 中所述进行滤波。

- 针对 3V 终端,RF-DAC 输出电流摆幅必须设置为 32 mA。

- 赛灵思建议将 VCCINT_AMS 连接到 VCCBRAM。

- VCCSDFEC 必须连接到 VCCBRAM。

3 推荐工作温度

4 可用速度等级与工作电压

5 电源时序

5.1 PS 上电/断电电源排序

低功耗域 (LPD) 正常运作后,全功耗域 (FPD) 方可正常运行。低功耗域和全功耗域可同时上电。按上电顺序运行期间,PS_POR_B 输入必须断言为 GND(请参阅表 37)。使用 FPD 时,它必须先上电,然后才能释放 PS_POR_B。

1 此处列出的低功耗域 (LPD) 推荐上电顺序旨在实现最低电流汲取并确保上电时 I/O 处于三态状态。推荐的断电顺序与上电顺序相反。

- VCC_PSINTLP

- VCC_PSAUX、VCC_PSADC 和 VCC_PSPLL,按任意顺序或同时执行。

- VCCO_PSIO

此处列出的全功耗域 (FPD) 推荐上电顺序旨在实现最低电流汲取并确保上电时 I/O 处于三态状态。推荐的断电顺序与上电顺序相反。

- VCC_PSINTFP 和 VCC_PSINTFP_DDR 从相同供电电源驱动。

- VPS_MGTRAVCC 和 VCC_PSDDR_PLL,按任意顺序或同时执行。

- VPS_MGTRAVTT 和 VCCO_PSDDR,按任意顺序或同时执行。

5.2 PL 上电/断电电源排序

推荐上电顺序为 VCCINT、VCCINT_IO/VCCBRAM、VCCAUX/VCCAUX_IO 和 VCCO,这样即可实现最低电流汲取并确保上电时 I/O 处于三态。推荐的断电顺序与上电顺序相反。如果 VCCINT 和 VCCINT_IO/VCCBRAM 的推荐电压电平相同,那么可使用相同电源为其供电并同步执行缓升。VCCINT_IO 必须连接到 VCCBRAM。如果 VCCAUX/VCCAUX_IO 和 VCCO 的推荐电压电平相同,那么可使用相同电源为其供电并同步执行缓升。VCCAUX 和 VCCAUX_IO 必须连接在一起。VCCADC 和 VREF 可随时上电,无上电顺序要求。VADC_AVCC、VADC_AVCCAUX、VDAC_AVCC、VDAC_AVCCAUX 和 VDAC_AVTT 可随时上电,无上电顺序要求。

为 GTY 收发器实现最小电流汲取的推荐上电顺序为 VCCINT、VMGTAVCC、VMGTAVTT 或 VMGTAVCC、VCCINT、VMGTAVTT。针对 VMGTVCCAUX不存在推荐的排序。VMGTAVCC 和 VCCINT 均可同时执行电源缓升。推荐的断电顺序与实现最小电源汲取的上电顺序相反。如果不满足这些推荐的顺序,那么上电和断电期间从 VMGTAVTT 汲取的电流可能高于相应的规格。

5.3 PS-PL 电源排序

PS 和 PL 电源为彼此完全独立的电源。所有 PS 电源均可在任意 PL 电源之前或之后上电。PS 和 PL 电源区域已隔离以防止损坏。

6 GTY 收发器

6.1 GTY 收发器 DC 输入电平和输出电平

说明:

## 6.2 GTY 收发器时钟输出电平规格

## 6.2 GTY 收发器时钟输出电平规格 文章来源:https://www.toymoban.com/news/detail-436292.html

文章来源:https://www.toymoban.com/news/detail-436292.html

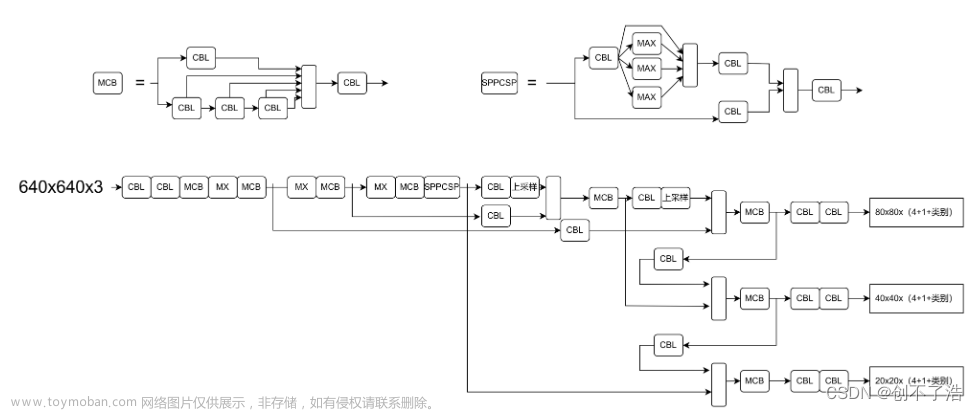

7时序控制方式

1 使用时序芯片

2 利用电源芯片的PG引脚控制上电的时序

欢迎一起讨论技术问题,求关注!文章来源地址https://www.toymoban.com/news/detail-436292.html

到了这里,关于FPGA选型--电源设计(详细讲解了电源设计过程)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!