FPGA基础知识---lattice莱迪斯深力科MachXO2 LCMXO2-4000HC-4TG144I FPGA简介

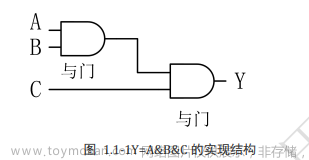

FPGA基础知识:FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

lattice莱迪斯深力科 超低密度FPGA 是最新的立即启用、非挥发性、小型覆盖区 FPGA,采用先进的封装技术,能让每个元件达到最低成本。此系列采用最新的小型封装,不仅具有低功率、成本优势并结合快速效能。FPGA 现场可编程逻辑器件,小尺寸,高性能!在工业领域,它可以用于网络控制器,PLC,网络边缘计算,机器视觉和工业机器人,ADAS/驾驶员辅助系统,汽车解决方案是FPGA的潜在应用领域。

适用于低成本的复杂系统控制和视频接口设计开发,满足了通信、计算、工业、消费电子和医疗市场所需的系统控制和接口应用。

瞬时启动,迅速实现控制——启动时间小于1mS,在上电时迅速控制信号,以确保出色的系统性能和可靠的运行。

通过内部逻辑提升系能性能——内置硬件加速逻辑和高达6864 LUT4

更多电压选择,节省更多成本——拥有3.3/2.5V和1.2V内核电压选择,待机功耗低至22μW

附上MachXO2 FPGA系列型号参考:

LCMXO2-256HC-4TG100C LCMXO2-640HC-4SG48I LCMXO2-1200HC-4TG100C LCMXO2-1200HC-4TG100I LCMXO2-1200HC-4TG144I LCMXO2-2000HC-4TG100C LCMXO2-2000HC-4TG144I LCMXO2-2000HC-4FTG256I LCMXO2-4000HC-4BG256I LCMXO2-4000HC-4TG144C LCMXO2-4000HC-4TG144I LCMXO2-4000HC-6MG132I LCMXO2-4000HC-6BG256I LCMXO2-7000HC-4TG144C LCMXO2-7000HC-4FG484C

特性:

高达256 Kbit的用户闪存和240 Kbit sysMEMTM嵌入式块RAM

高达334个可热插拔的IO,可防止额外漏电

通过JTAG、SPI和I2C和Wishbone进行编程

TransFR功能支持现场设计升级,无需中断设备运行

可编程sysIOTM缓冲器支持LVCMOS、LVTTL、PCI、LVDS、LVDS、MLVDS、RSDS、 LVPECL、SSTL、HSTL等接口

文章来源:https://www.toymoban.com/news/detail-437286.html

文章来源:https://www.toymoban.com/news/detail-437286.html

文章来源地址https://www.toymoban.com/news/detail-437286.html

到了这里,关于快进来,带你了解FPGA基础知识---lattice莱迪斯深力科MachXO2 FPGA系列简介的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!