文章简介

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

第十五章:VGA

VGA(Video Graphics Array)视频图形阵列是IBM于1987年提出的一个使用模拟信号的电脑显示标准。VGA接口即电脑采用VGA标准输出数据的专用接口。VGA接口共有15针,分成3排,每排5个孔,显卡上应用最为广泛的接口类型,绝大多数显卡都带有此种接口。它传输红、绿、蓝模拟信号以及同步信号(水平和垂直信号)。

它具有分辨率高、显示速率快、颜色丰富等优点。VGA接口不但是CRT显示设备的标准接口,同样也是LcD液晶显示设备的标准接口,具有广泛的应用范围。

很多人觉得只有HDMI接口才能进行高清信号的传输,但这是一个大家很容易进入的误区,因为通过VGA的连接同样可以显示1080P的图像,甚至分辨率可以达到更高,所以用它连接显示设备观看高清视频是没有问题的,而且虽然它是种模拟接口,但是由于VGA将视频信号分解为R、G、B三原色和HV行场信号进行传输,所以在传输中的损耗还是相当小的。

首先我们看一下 VGA 接口的电路原理图:

图1 VGA接口原理图

通过图1可以看出VGA 并没有特殊的外部芯片,也就是说,唯一要关注的就是它的显示原理和时序了。那么接下来我们具体来看一下VGA 的扫描原理是什么。

VGA扫描方式:

显示器扫描方式分为逐行扫描和隔行扫描:①逐行扫描是扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行, 电子束回到屏幕的左边下一行的起始位置,在这期间, CRT 对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

② 隔行扫描是指电子束扫描时每隔一行扫一线,扫完一屏后再返回来扫描剩下的线。

图2 VGA图像显示扫描示意图

常见的彩色显示器一般由 CRT(阴极射线管)构成,色彩是由 R、 G、 B(红、黄、蓝)三基色组成。显示是用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生 RGB 三基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,进行扫描, 每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这其间 CRT 对电子束进行消隐。每行结束时,用行同步信号进行同步;扫描完所有行,用场同步信号进行同步,并使扫描回到屏幕左上方,同时进行场消隐,预备下一场的扫描。

对于普通的 VGA 显示器,共有 5 个信号:R、 G、 B 三基色;HS(行同步信号);VS(场同步信号)。对于时序驱动, VGA 显示器要严格遵循“VGA”工业标准,即 640x480@60Hz 模式,否则可能会损害 VGA 显示器。

了解了扫描原理后,紧接着看一下 VGA 的行、列同步时序:

图3 列同步时序

图4 行同步时序

VGA 中定义行时序和列时序都需要同步脉冲(a 段),显示后沿(b 段)、显示时序段(c 段)和显示前沿(d 段)四部分。VGA 工业标准显示模式要求:行同步、列同步都为负极性,即同步脉冲要求是负脉冲。

由 VGA 行时序可知:每一行都有一个负极性行同步脉冲(a 段),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿(b 段),在显示时序段(c 段)显示器为亮的过程, RGB 数据驱动一行上的每一个像素点,从而显示一行。在一行的最后为显示前沿(d 段)。在显示时间段之外没有图像

投射到屏幕,而是插入消隐信号。同步脉冲、显示后沿和显示前沿都是在行消隐间隔内,当消隐有效时,RGB 信号无效,屏幕不显示数据。

各分辨率下,VGA的显示标准参数如图5所示:

图5 VGA标准参数

本实验以显示标准为 800*600*60Hz 为例。(800 为列数, 600 为行数,60Hz 为刷新一屏的频率)。

行时序:屏幕对应的行数为 628(a+b+c+d=e 段),其中 600(c 段)为显示行;每行均有行同步信号(a 段),为 4 个行周期的低电平;

列时序:每个显示行包括 1056 列(a+b+c+d=e 段),其中 800(c 段)为有效显示区,每一行有一个行同步信号(a 段),为 128 个行周期的低电平。

扫描时钟频率:40MHZ。

原理清楚以后,接下来设计系统模块图如下:

图6 系统模块框图

模块说明:

(1)时钟分频模块

开发板上使用的晶振为 50MHZ,由于我们的显示标准为 800*600*60HZ,所以需要分频输出 40MHZ 的系统时钟。时钟分频模块,我们可以通过调用锁相环来实现。

(2)VGA 行列同步控制模块

VGA 显示标准需要设定行列同步信号,标定出有效显示区域, 这也是整个 VGA驱动模块的核心部分。

(3)VGA 色彩显示控制模块

在图像有效显示区域内,输出控制颜色的 r、 g、 b 信号。接下来学习每个功能模块的具体代码实现,分频模块采用锁相环实现即可。

VGA 行列同步控制模块具体代码如下:

VGA 色彩显示控制模块具体代码如下:

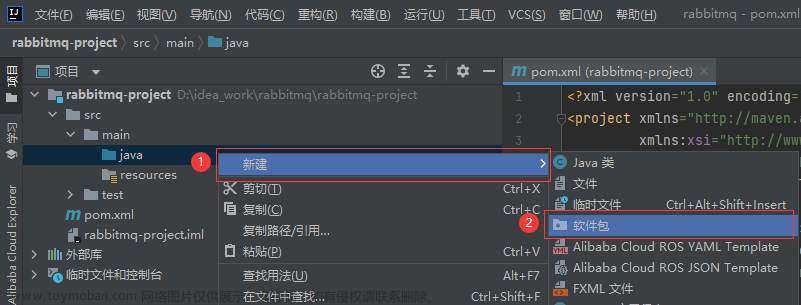

编写完成各子模块以后,将所有模块连接起来,需要建立顶层文件如下:

综合编译以后,我们可以查看 RTL 视图,查看电路综合结果和预想是否一致,调用 RTL 视图如下:

图7 RTL视图

通过RTL图可以看出电路模块综合结果和预先设计的系统模块框图相同。接着编写测试代码如下,用来验证我们设计的正确性:

通过Modelsim仿真,查看仿真波形:

可以看出,当 en 有效时, vga_r 输出 3’ b111,说明设计正确。

编写管脚约束文件,生成bit文件,将bit文件下载到开发板,实际运行效果图如下:

文章来源:https://www.toymoban.com/news/detail-438273.html

文章来源:https://www.toymoban.com/news/detail-438273.html

图8 显示结果 文章来源地址https://www.toymoban.com/news/detail-438273.html

到了这里,关于FPGA入门系列14--VGA的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!