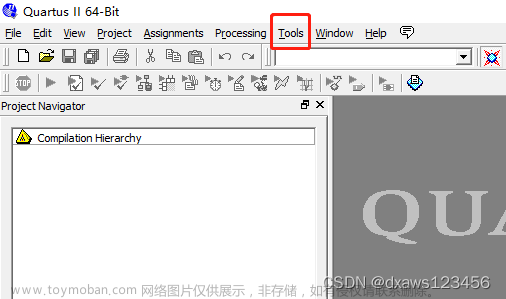

首先打开quartus中的PD平台,点击左上角file,选择new component

填写ip核名称,以及展示名称

点击file选项卡,然后在文件夹中选择我们需要的封装的文件

然后点击编译分析文件

然后点signal&interfaces选项卡

将as里的信号拉入avalon选项中,同时移除as选项

点击add interface,添加reset input端口,同时将rst_n拉到reset input端口中,在右边选项卡中,single type选择为rst_n

点击add interface,添加conduit端口,同时将输出端口,o_pwm拉到conduit端口中, 在右边选项卡中,single type选择为reg

针对下面问题框中的问题

第一条:Error: avalon_slave_0: Cannot have both write and writebyteenable (only one is allowed)

解决办法:在avalon_slave选项中,点击as_write_data选项,右方选项卡中,signal type改为writedata

第三个问题:Error: avalon_slave_0: Interface must have an associated reset

解决办法:点击avalon_slave选项,右方选项卡中,将associated Reset改到reset_slink

直到描述框中显示

代表我们配置完成,然后点击finish

ip核调用框出现我们封装好的ip,就代表我们封装完成,这个时候我们就可以像正常ip核一样,对他进行调用即可,详情参照“SOC添加外设(添加按键和点灯)”文章来源:https://www.toymoban.com/news/detail-439178.html

文章来源地址https://www.toymoban.com/news/detail-439178.html

文章来源地址https://www.toymoban.com/news/detail-439178.html

到了这里,关于Quartus 18.1 PD平台封装IP核的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!