🎉欢迎来到FPGA专栏~Verilog文件的基本结构

- ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹

- ✨博客主页:小夏与酒的博客

- 🎈该系列文章专栏:FPGA学习之旅

- 文章作者技术和水平有限,如果文中出现错误,希望大家能指正🙏

- 📜 欢迎大家关注! ❤️

Verilog HDL系列博客参考书籍 《Verilog HDL设计实用教程》 和小梅哥教学视频。该系列博客将会融合两部分参考内容,总结知识点,帮助新手快速掌握Verilog HDL。

一、Verilog模块的基本结构

实现一个2-4译码器的Verilog代码:

//2-4译码器的Verilog代码

module decode2x4(Z,A,B,Enable);

output [3:0]Z;

input A,B,Enable;

wire A_n,B_n;

not V0(A_n,A);

not V1(B_n,B);

nand N0(Z[3],Enable,A,B);

nand N1(Z[0],Enable,A_n,B_n);

nand N2(Z[1],Enable,A_n,B);

nand N3(Z[2],Enable,A,B_n);

endmodule

上述代码编写了一个2-4译码器的模块,基本包含了所有Verilog代码的通用结构。该模块的代码由四部分组成:模块定义、端口声明、内部资源声明和功能描述。

模块定义部分的代码:

//2-4译码器的Verilog代码

module decode2x4(Z,A,B,Enable);

...

endmodule

端口声明部分的代码:

output [3:0]Z;

input A,B,Enable;

内部资源声明部分的代码:

wire A_n,B_n;

功能描述部分的代码:

not V0(A_n,A);

not V1(B_n,B);

nand N0(Z[3],Enable,A,B);

nand N1(Z[0],Enable,A_n,B_n);

nand N2(Z[1],Enable,A_n,B);

nand N3(Z[2],Enable,A,B_n);

需要记住一个Verilog模块由四个部分组成。模块定义、端口声明、内部资源声明和功能描述四个部分构成一个完整的模块。

二、语法详细介绍

2.1 模块定义

模块的定义以关键字module开始,以关键字endmodule结束,在这两个关键字之间的代码被识别为一个模块,即一个具有某种基本功能的电路模型,其基本语法结构如下:

//模块的定义

module 模块名(端口名1,端口名2,端口名3,...);

...

endmodule

对于Verilog模块的定义需要注意如下三点:

🔸第一点: 一个Verilog文件中可以定义多个模块,但是为了便于文件的管理和模块的调用,一般情况下一个Verilog文件中只定义并编写一个模块。

//一个Verilog文件中定义多个模块

module mux2(a,b,sel,out,io);

...

endmodule

module mux4(a,b,sel,out,io);

...

endmodule

module mux8(a,b,sel,out,io);

...

endmodule

...

🔸第二点: 在定义模块的同时,需要自己定义模块名和端口名。而对于端口名的写法,常用的有两种。

//第一种写法

module mux2 (a,b,sel,out,io)

//端口属性定义

input [7:0] a;

input [7:0] b;

input sel;

output [7:0] out;

inout io;

...

endmodule

//第二种写法

//Verilog对于端口列表的新写法

module mux2 (

//端口属性定义

input [7:0] a,

input [7:0] b,

input sel,

output [7:0] out,

inout io

);

...

endmodule

第二种写法将端口的类型(属性)直接写到了端口名部分。推荐使用第二种写法,便于管理、检查和调用。

使用第二种写法编写2-4译码器:

//2-4译码器的Verilog代码

module decode2x4(

output [3:0] Z,

input A,

input B,

input Enable

);

wire A_n;

wire B_n;

not V0(A_n,A);

not V1(B_n,B);

nand N0(Z[3],Enable,A,B);

nand N1(Z[0],Enable,A_n,B_n);

nand N2(Z[1],Enable,A_n,B);

nand N3(Z[2],Enable,A,B_n);

endmodule

🔸第三点: 模块的名称、端口的名称等需要自己来定义的名称,统称为标识符。

标识符使用的规则:

- 标识符区分大小写,例如:Cnt和cnt是不同的。

- 标识符的第一个字符必须是字母或下画线,不能以数字或美元符开始。

- Verilog基本语法中使用到的关键字作为保留字,是不能用作标识符的。

2.2 端口声明

端口声明,即给出端口的具体信息,包括输入输出和位宽情况。

端口的类型有三种,分别是:input、output和inout:

| 端口类型 | 关键字 |

|---|---|

| 输入端口 | input |

| 输出端口 | output |

| 双向端口 | inout |

端口定义时默认一位宽度,即只能传播一位信号。

指定端口的位宽:

端口类型 [端口位宽左界:端口位宽右界] 端口名

例如:

module mux2 (

//端口属性定义

input [7:0] a,

input [7:0] b,

input sel,

output [7:0] out,

inout io

);

...

endmodule

2.3 内部资源声明

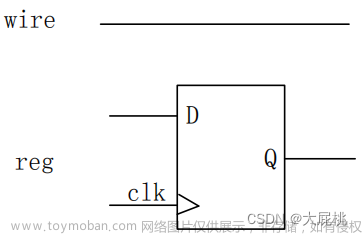

对于内部资源的声明,比较常见的是连线(线网)类型和寄存器类型。

🔸时序逻辑驱动的信号-寄存器类型reg。

🔸组合逻辑驱动的信号-线网类型wire。

需要在

always块中进行赋值时,必须定义为reg类型。

例如:

//定义内部信号

wire oe;

reg [7:0] y;

reg [7:0]shift_a;

always@(posedge clk)

shift_a <= {shift_a[0],shift_a[7:1]};

连线和寄存器的最初目的是描述电路中的连接线(就是导线)和寄存器(数字电路基本时序器件)。wire最后一定会变成连线,而reg则不一定真的会变成寄存器。

2.4 功能描述

功能描述部分是Verilog最主要的一个部分。

功能描述部分就是要完成该模块能实现的功能。该部分会在后续的文章中逐步讲解。

三、其余基础语法

3.1 assign语句简单介绍

assign语句,即连续赋值语句。

对于二选一多路器的功能描述,如下的assign语句都是等价的:

//连续赋值语句

assign out = (sel == 0)?a:b;

//简化写法

assign out = !sel?a:b;

//等价写法

assign out = sel?b:a;

FPGA实现二选一多路器链接:【FPGA零基础学习之旅#2】“二选一多路器”简单实例

assign语句实现三态门的控制:

//三态门控制

inout io;

assign oe = sel;

assign io = oe?out[0]:1'bz;//z表示高阻态,高阻态表示输入

3.2 位操作

🔸对于数据的表示:

//位宽的表示

//数据的表示

assign x = 4'b1001;//1001(2)=9(10)

assign x = 4'd9;

assign x = 4'h9;

assign x = 4'hc;

assign n = 32'h1234_4567;

assign z = 8'b1001_1011;

在上述代码的例子中,如assign x = 4'b1001;//1001(2)=9(10),4表示数据的位宽,b表示数据类型为二进制数,1001即为数据(二进制的1001等于十进制的9)。

b表示二进制;d表示十进制;h表示十六进制。位宽与进制之间用 ’ 分隔开。

🔸对于位的操作:

这里介绍Verilog中的三种位操作:取某一位直接用作数据源、循环移位操作和位拼接操作。

- 取某一位直接用作数据源:

//取某一位直接用作数据源

output [7:0] out;

wire [2:0]m;

assign m = out[5:3];

- 循环移位操作:

//循环移位操作

reg [7:0]shift_a;

always@(posedge clk)

shift_a <= {shift_a[0],shift_a[7:1]};

- 位拼接操作:

//位拼接操作,“{}”表示拼接

wire [3:0]x;

wire [3:0]y;

wire [7:0]z;

wire [31:0]n;

assign z = {x,y};

//下面两种写法等效

assign n = {y,7{x}};

assign n = {y,x,x,x,x,x,x,x};

文章来源:https://www.toymoban.com/news/detail-439972.html

文章来源:https://www.toymoban.com/news/detail-439972.html

🧸结尾文章来源地址https://www.toymoban.com/news/detail-439972.html

- ❤️ 感谢您的支持和鼓励! 😊🙏

- 📜您可能感兴趣的内容:

- 【FPGA-Spirit_V2】基于FPGA的循迹小车-小精灵V2开发板

- 【Go黑帽子】使用Golang编写一个TCP扫描器(高级篇)

- 【Arduino TinyGo】【最新】使用Go语言编写Arduino-环境搭建和点亮LED灯

- 【Labview-3D虚拟平台】Labview与Solidworks联合仿真(保姆级)(下)装配体、父级与子级

到了这里,关于【Verilog HDL】FPGA-Verilog文件的基本结构的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!