第1关:基本SR锁存器的设计

任务描述

本关任务:在Logisim中,构建由两个或非门构成的基本SR锁存器。

第2关:门控SR锁存器的设计

任务描述

本关任务:在Logisim中,在基本锁存器的基础上构建门控SR锁存器。

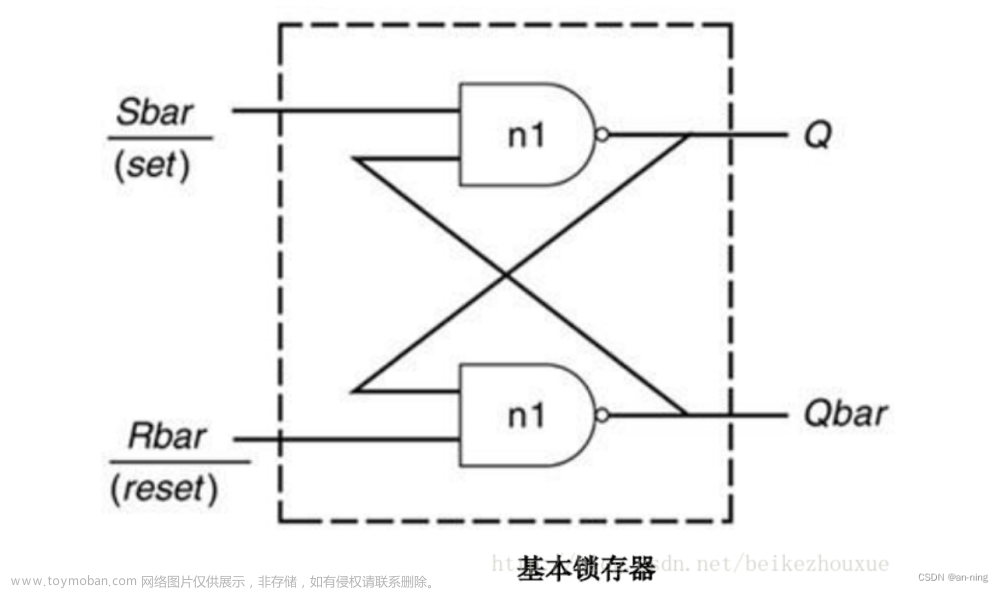

第3关:与非门构成的门控SR锁存器的设计

任务描述

本关任务:在Logisim中,用四个与非门构建门控SR锁存器。

第4关:门控D锁存器的设计

任务描述

本关任务:在Logisim中,用四个与非门构建门控D锁存器。

第5关:主从D触发器的设计

任务描述

本关任务:在Logisim中,用两个D锁存器级联构建主从式D触发器,要求下降沿触发。

第6关:T触发器的设计

任务描述

本关任务:在Logisim中,在D触发器的基础上构建T触发器,要求时钟上升沿触发

第7关:JK触发器的设计

任务描述

本关任务:在Logisim中,在D触发器的基础上构建JK触发器,要求时钟上升沿触发。

文章来源:https://www.toymoban.com/news/detail-441113.html

文章来源地址https://www.toymoban.com/news/detail-441113.html

到了这里,关于educoder数字逻辑实训:锁存器和触发器设计(Logisim)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!