一、物理层PHY介绍

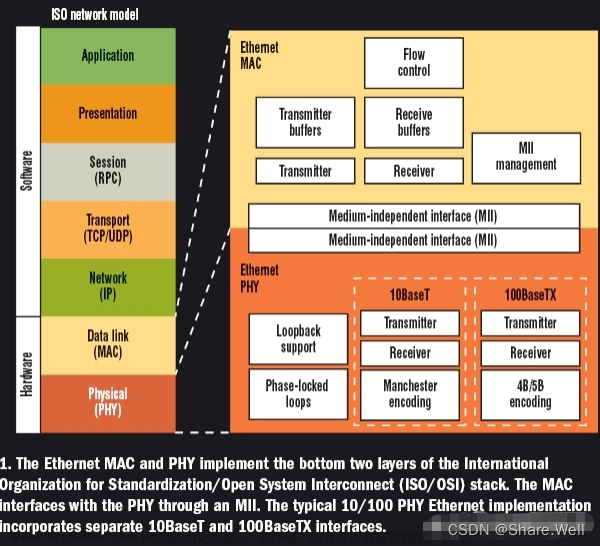

1、PHY(物理层):

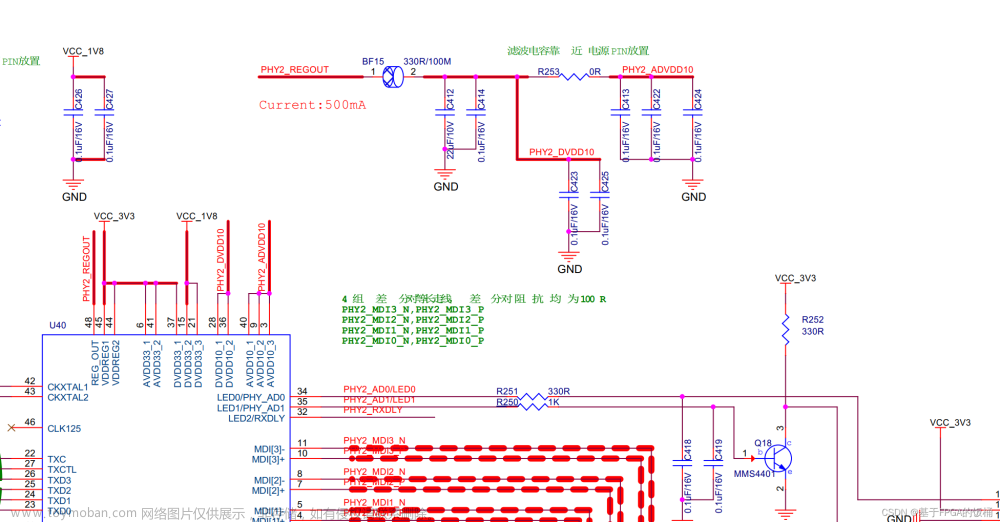

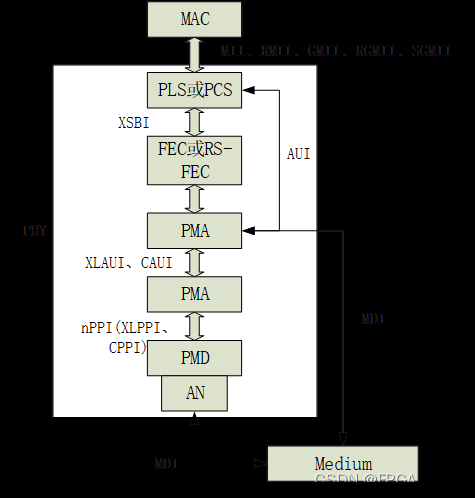

MII/GMI/RMII/RGMII/SGMIII(介质独立接口子层),PLS/PCS(物理编码子层),PMA(物理介质连接子层),PMD(物理介质相关子层),AN(自动协商),MDI(媒介相关接口)。

2、PLS/PCS(物理编码子层):

(PLS)对 MAC 给的信息进行传递,只在IMb/s、10Mb/s 的应用场景才出现;(PCS)对MAC给的信息进行编码,应用于>100 Mb/s的应用场景,比如完成 8B/10B、64B/66B、256B/257B编码。

3、PMA(物理介质连接子层):

执行信号的并串/串并转换。

4、PMD(物理介质相关子层):

信号转换到特定介质上或反向转换,负责将串行信号转到相应的物理介质上。

5、AN(自动协商):

自协商一般是在物理层完成的,但是具体在PHY的哪一层完成,由具体物理介质规范决定。基本原理就是将自协商的信息通过一串脉冲序列发送出去,这串脉冲称为FLP。

6、MDI接口:

MDI层和物理媒质的接口,是串行比特的物理接口,MDI就是连接PHY芯片和物理介质的接口,常见的是RJ45接口。百兆网时,MDI四根线,两对差分信号,只用了RJ45的 1,2,3,6线;千兆网时MDI一共8根线,四对差分信号, 用了RJ45的8根线。RJ45上的两个灯,绿灯长亮表示链路完整,黄灯闪烁表示有数据收发。

7、AUI:

是PCS与PMA之间的接口连接。

二、SGMI在以太网中的应用

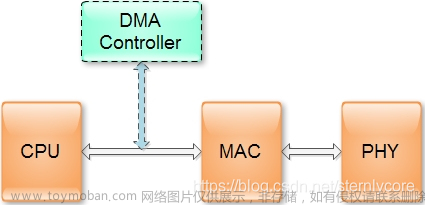

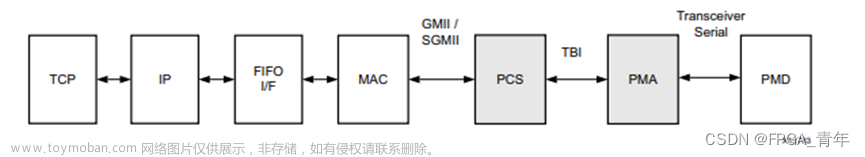

SGMII本质上并没有对以太网协议的分层做改动,还是MAC层,PCS层和PMA层。原来GMII模式下,MAC层一般做在FPGA侧,PHY层包括PCS+PMA做在另一个单独的芯片上。而SGMII的实施是将PCS层也同时放在了原来的MAC侧。这样FPGA芯片和PHY芯片各有一个PCS层。

对于FPGA发送来说,数据包有MAC层过来,经过tx 的pcs,从SGMII接口发送出去。在PHY芯片上,有一个rx的pcs先将SGMII的信号解出GMII信号,然后再经过传统的PHY层处理发送到介质上。对于FPGA接收来说,则反过来。

三、以太网中使用GT高速接口

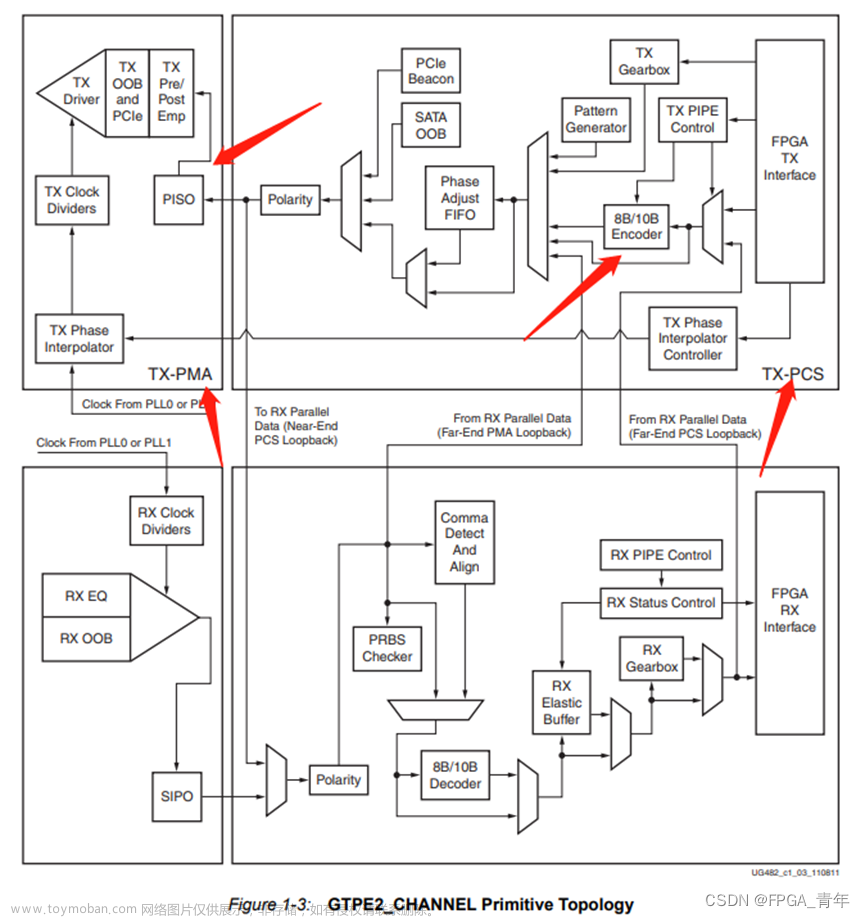

GTx接收和发送方向均由PCS和PMA两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码等;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重与均衡。

不同系列的GTx,集成的PCS和PMA的功能不一样,越高端的系列,集成的功能越多,传输的速率越快。下表为最新的GTY集成的PCS和PMA的功能。

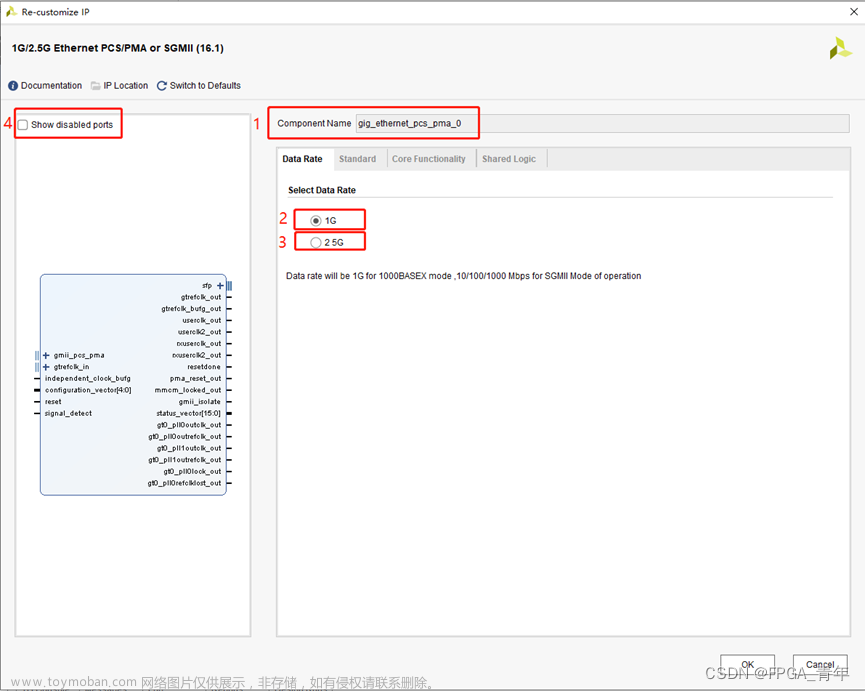

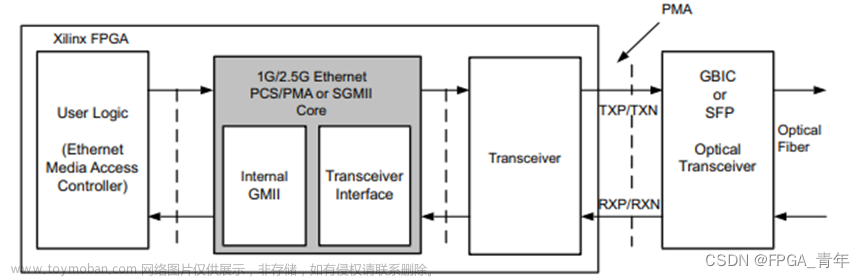

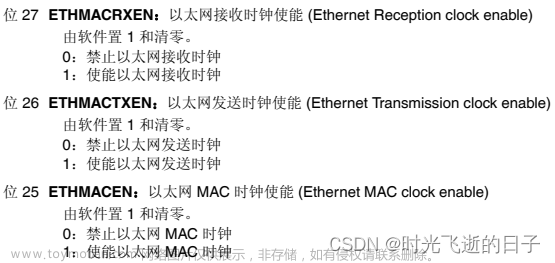

在使用FPGA的以太网IP核1G/2.5G Ethernet PCS/PMA or SGMII时,采用的时高速接口,与对端的PHY连接采用的是TX/RX串型接口。而在使用Tri Mode Ethernet MAC IP核时候,则是采用的RGMII。

参考文章

上图是以太网IP核1 Gigabit Ethernet PCS and PMA网络体系,MAC层和右侧的所有子层在IEEE 802.3-2008规范中有定义。

上图是以太网测试高速接口GTP的内部连接,里边分为两大部分,PCS层(Physical Coding Sublayer,物理编码子层)和PMA层(Physical Media Attachment,物理媒介适配层),PCS层主要完成编码工作,PMA层主要完成的是串并转换工作。

以太网之物理层 - SevenFormer - 博客园 (cnblogs.com)

PHY(Physical Layer,PHY) - 知乎 (zhihu.com)

SGMII协议解析_sgmii接口_poena的博客-CSDN博客文章来源:https://www.toymoban.com/news/detail-441637.html

记录美好学习,从总结开始;💪文章来源地址https://www.toymoban.com/news/detail-441637.html

到了这里,关于FPGA平台以太网学习:MAC与PHY间通信的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!