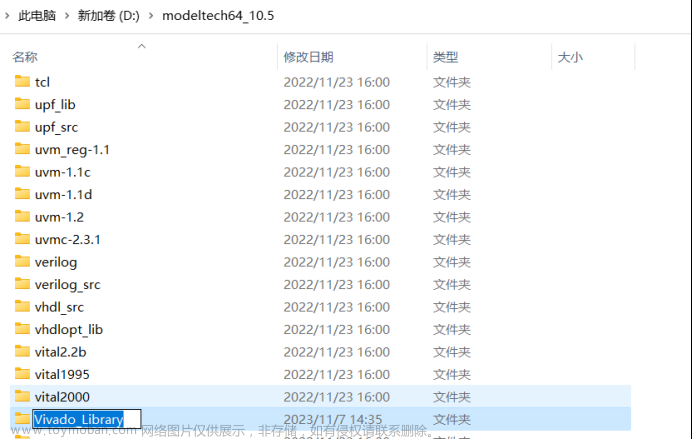

vivado创建的工程文件中不同后缀文件夹内容说明

如上图所示,Vivado工程文件中包含的各个类型文件具体可分为:

project_name.cache:Vivado 软件的运行缓存

project_name.hw: 所有波形文件

project_name.ip_user_files:用户关于 IP 的文件

project_name.runs:编译与综合结果 \impl_1 文件夹中的.bin 和 .bit 即为编译生成的可执行文件

project_name.sdk:SDK 环境代码,一般是 ZYNQ 设计中关于 PS 端的代码

project_name.sim:仿真结果

project_name.srcs:所有用户编写的源码、仿真文件与约束文件

project_name.xpr: Vivado 工程启动文件

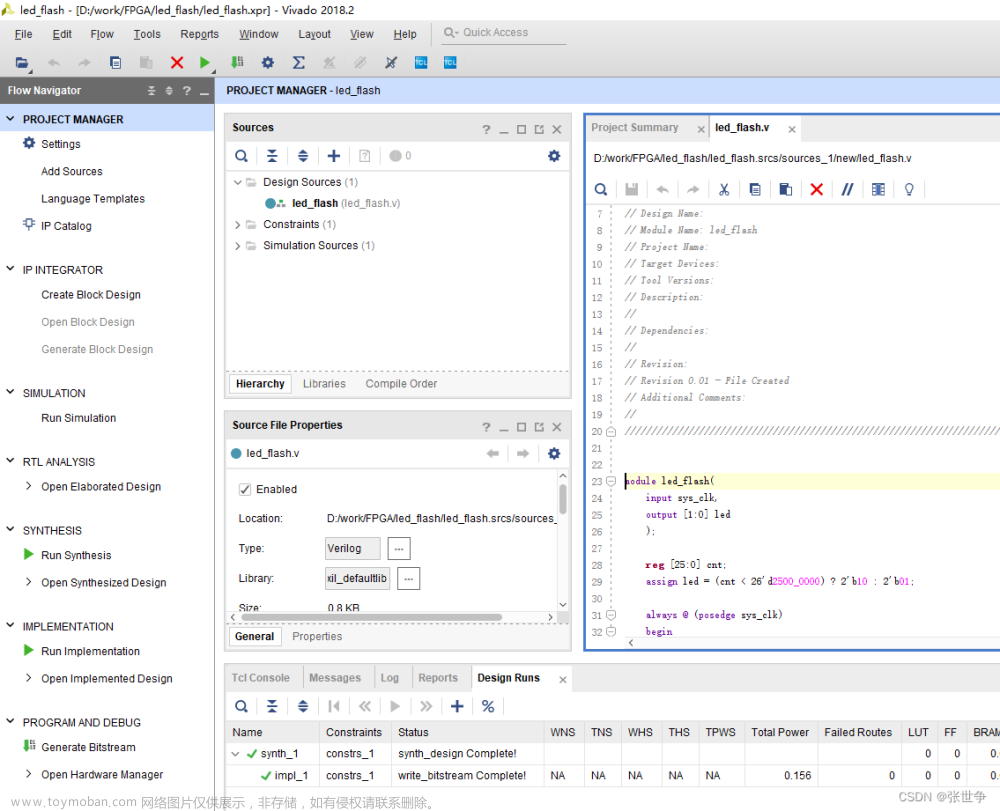

1、.dcp文件,在ise中每个过程都会产生特定格式的文件,例如.ncd, .pcf, .ngd等等,但是在vivado中,不论是综合还是布局布线都只会产生一种格式的文件,即.dcp文件,每个阶段的.dcp文件都是下一阶段的输入文件,.dcp文件实际上包含了对应阶段处理的信息,用vivado可以直接打开,File->Open Checkpoint. dcp文件主要包括Physical Constraints, Device Constraints, Netlists以及device的信息。

2、.xdc文件,这个是vivado的约束文件。

3、.xci文件,这是定制ip产生的文件,里面包含了定制的ip核的所有信息。

4、.rpt文件,这个是每个过程结束输出的一个report文件,用来记录各个过程中的一些信息。

其中:比较有用的文件是.src文件和.xpr文件,.src存放用户编写的所有源代码,.xpr是vivado的启动文件。文章来源:https://www.toymoban.com/news/detail-442462.html

参考链接:https://blog.csdn.net/m0_37779673/article/details/120587541文章来源地址https://www.toymoban.com/news/detail-442462.html

到了这里,关于Vivado 工程文件内容说明的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!