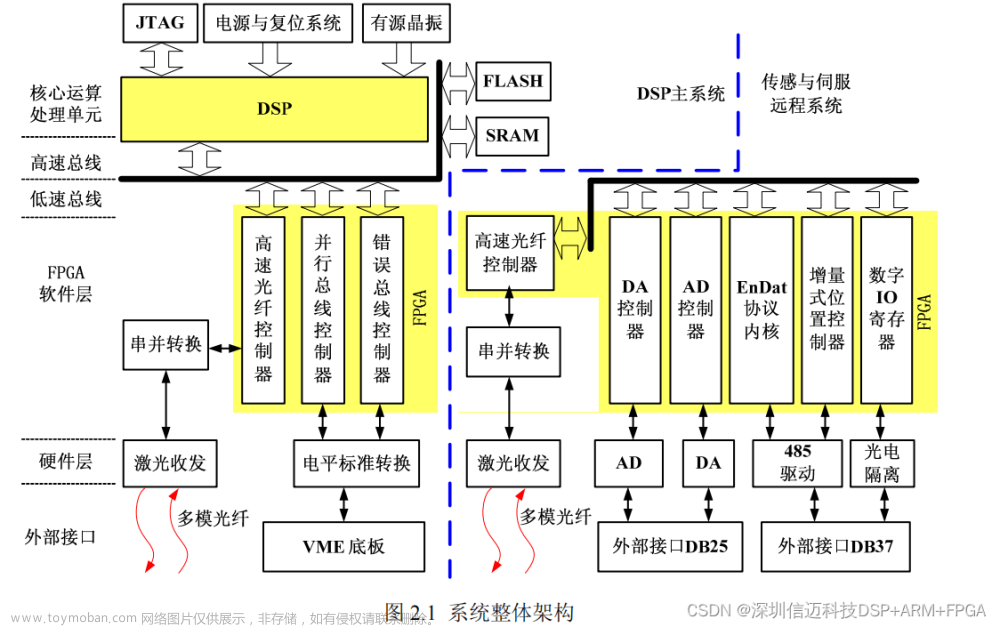

这篇具有很好参考价值的文章主要介绍了基于dsp+fpga的半导体运动台高速数据采集FPGA endac设计(三)。希望对大家有所帮助。如果存在错误或未考虑完全的地方,请大家不吝赐教,您也可以点击"举报违法"按钮提交疑问。

EnDat

双向串行通信协议的实现

数据(测量值或参数)可以在位置编码器和

EnDat

协议内核之间进行双向传输,

EnDat

协议内核的收发单元支持

RS-485

差分信号传输,数据传输与传感伺服控制系统

生成的时钟脉冲同步。传输的数据类型(位置值、参数或诊断信息等)通过

EnDat

协议

内核发至编码器的模式指令选择。

EnDat

数据接口是海德汉公司为编码器设计的双向数

字接口,具有高性能、低成本等一系列重要优点比如低成本、高质量、支持先进机床设

计原则等等

[42-44]

。

为匹配线路特征阻抗(Characteristic Impedance),在数据和时钟的差分线路端部,

各需加一个

120

Ω的电阻,同时各线路应加一个

330pF

的电容,以滤除高频干扰。

EnDat

串行通信模型见图

4.20

所示。

EnDat 2.2

版对

EnDat 2.1

具有很好的兼容性,性能得到进一步提升。主要表现在

1

)

更高时钟频率;

2

)更短计算时间;

3

)更短恢复时间

4

)更宽供电电压。

4.6.1 线路传输延时补偿

EnDat

串行通信模型中的时钟脉冲用于同步数据传输。时钟频率是可以通过应用层

DSP

系统进行主动配置的

,

频率可在

100 kHz

到

16 MHz

之间变化。时钟频率取决于电

缆长度。线缆长度不断增加或是时钟频率不断提高,传输延时与有效数据到达一个尺度,

无法区分两者区别,必须测量延迟时间并加以补偿。无延时补偿情况下最大频率可达

2

MHz

[43]

。在有补偿的情况下,最大时钟频率可达到

16 MHz

。线缆长度跟时钟频率的关

系曲线见图

4.21

[46]

所示。

线路传输延时补偿,在更换传输线硬件设备后必须重新计算,为保险起见,最好每

次开机进行第一次数据传输之前,自动确定线路延时自动补偿。

具体的补偿方法是这样的,每次上电后

EnDat

协议内核给编码器发送模式指令“编

码器传输无附加信息的位置值”。这个补偿过程不受上面应用层的控制,由

EnDat

协议

内核自动完成。由

EnDat

协议内核发送指令模式完毕后,

EnDat

协议内核便开始记录时

钟的每一个上升沿。最后一次检测到时钟上升沿与起始标志位

start

之间的时间间隔,定

义为传输延时

t

D

。

为了保证测量得到的延时时间可靠,需采用三次测量取平均值的方法。且三次测得

的传输延时时间不应大于最大传输时时钟周期的八分之一。测量过程所用时钟频率与正

常传输时不同,采用

100 kHz

较低时钟频率来进行测量信号传输延时时间。且为了达到

足够高精度,传输延时时间的内部频率必须是数据传输时钟频率的八倍以上。

4.6.2 传输数据类型及模式指令

数据类型包括三种类型,它们分别是位置值、附加信息及参数。模式指令包括三个

比特位。

EnDat

协议内核在传输时钟的下降沿同步发送模式指令的每一位,而编码器则

在传输时钟的上升沿同步接收模式指令比特位。为确保可靠的传输模式指令的比特位,

每个比特位均采取取反的方式或者重复发送的方式。

为保证通信的正常运行,在有线路传输延时补偿的情况下,每一次数据传输过程中,

第一个时钟必须维持不小于

2 µs

的低电平。

EnDat

模式指令系统如表

4.2

[43]

所示。

从表格

4.2

中也可以明显的看出,

EnDat 2.1

是

EnDat 2.2

指令集的子集,所以任何

适用于

EnDat 2.1

模式指令,必定适用于

EnDat 2.1。

4.6.3 位置值数据传输格式及 CRC 校验

传输周期从第一个时钟下降沿开始,两个时钟脉冲(

2T

)后,

EnDat

协议内核发送

000111

指令码,编码器成功接收到指令码后,开始向内核发送位置数据。首先发送起始

标志位,接着发送“

ERR1

”和“

ERR2

”错误指示信号,用以指示故障是否已经发生。

然后发送有效的位置数据。有效的位置数据以最低有效位开始,以最高有效位结束,具

体的位数由编码器的总长度参数决定,不同编码器总长度各不相同,可以被查询。

有效的位置数据结束后紧跟着就是循环冗余校验码部分。数据发送完毕后,信号线

被拉高为高电平,等待下一次新数据的传输。

带有附加信息的位置值传输格式见图

4.22

所示。其中,数据包内容包括错误信息

1

和

2

、位置值、附加信息

1

、附加信息

2

。

为了检测数据传输过程中由于干扰造成的传输错误,在位置值和附加信息后面采用

5

位的

CRC

校验码。在编码器端,

CRC

校验码由硬件生成。

EnDat

协议内核将接收

到的

CRC

码与之前接收到的串行数据流在本地生成的

CRC

码进行比较,即可检验通信

的正确与否。

CRC

校验可以检测出数据传输中的所有单一错误,是数据可靠传输的重要

保障

[41,45,47,49]

。

图

4.23

[43]

给出了编码器中

CRC

校验码的生成方案,因此,在本课题设计的

EnDat

协议内核中,也必须采用同样的

CRC

生成方案,才能保证

CRC

校验的正确性。由图

4.23

中可以看出,主要由一些逻辑门电路和触发器组成,因此在

FPGA

中利用

Verilog HDL

硬件描述语言来实现,非常方便简单,在此不再赘述。

4.6.4 EnDat 协议内核的 FPGA 实现

图

4.24

[48,50]

所示为

EnDat

协议内核的结构图,由时序控制模块、发送模块、接收模

块、时钟生成模块、相关寄存器及其与光纤通信内核的逻辑接口模块组成。

在内核结构图的左侧,是内核与同步串行双向接口的物理层接口信号,包括发送信

号线、接收信号线、时钟信号线及其各自的使能信号。在右侧,则是与光纤通信内核连

接的并行接口,包括了各种控制信号,

8

位的地址总线,

32

位的数据总线。其中地址总

线为

8

位宽度,对应于传输数据包格式中有效数据的个数被限定在

255

以内。

发送寄存器、模式指令寄存器和配置寄存器保存着待发送的数据。一旦触发,这些

数据被转为串行数据流在时序控制模块的控制下由发送模块串行发送给编码器,同时时

钟生成模块生成所需个数的时钟脉冲。接收模块在时序控制下将串行的数据流进行串并

转换,并将并行的数据,依据不同的含义,分配在

3

个寄存器中,同时更新状态寄存器

和中断寄存器,并产生中断或触发信号给光纤通信内核

[50]

。

根据

EnDat

协议规范,采用

5

位的循环冗余检验(

CRC

)码来完成串行通信的数据

校验功能。将接收到的

CRC

码与之前接收到的串行数据流在本地生成的

CRC

码进行比

较,即可检验通信的正确与否。

CRC

校验可以检测出数据传输中的所有单一错误,是正

确快速地获取位置值的保证。

CRC

校验结果保存在如图

4.24

所示的状态寄存器中。

4.6.5 位置值数据请求与传输机制

本课题中,最上层控制单元为

DSP

,所有的数据传输进程都受其控制。数据传输按

数据流的方向分为上行数据进程和下发数据进程。下发数据进程即

DSP

向

EnDat

内核

下发各种配置数据的过程;上行数据进程即

DSP

向位置获取模块发送请求位置数据的

过程,在此详细论述上行数据进程,下行数据进程与之类似,在此不再赘述。

DSP 下发请求位置数据命令,光纤通信内核 A 收到触发,发送请求数据字符 K28.2,即TTC 特殊字符。经过高速光纤通道,接收端光纤内核 B 收到该特殊字符,立即启动 文章来源:https://www.toymoban.com/news/detail-442528.html

EnDat

内核向位置编码器的位置请求过程,完成后开始向模块

A

按照图

4.25

所示的数据

包格式发送位置数据及相关状态信息,模块

A

接收完毕数据,产生中断,触发

DSP

读

取数据开始处理过程。

信迈提供FPGA Endat协议实现。文章来源地址https://www.toymoban.com/news/detail-442528.html

到了这里,关于基于dsp+fpga的半导体运动台高速数据采集FPGA endac设计(三)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处: 如若内容造成侵权/违法违规/事实不符,请点击违法举报进行投诉反馈,一经查实,立即删除!