FPGA中LPM_ROM定制与读出实验

一.实验目的

1.掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法;

2.用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于lpm_ROM中;

3.在初始化存储器编辑窗口编辑mif文件配置ROM;

4.验证FPGA中mega_lpm_ROM的功能。

二.实验原理

ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。

实验中主要应掌握以下三方面的内容:

1.lpm_ROM的参数设置;

2.lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写;

3.lpm_ROM的实际应用,在实验台上的调试方法。

三.实验步骤

1.建立工程:

A.新建一个存储器初始化(.mif)文件。

B.打开QuartusII,在顶部菜单中选File -> New other files ->memory initialization file ,单击OK,在弹出的对话框中输入字数64和字长8,单击OK, 打开存储器初始化编辑窗口。利用View菜单命令,改变地址或字长的显示格式等,选择要编辑的字(反白显示),直接输入内容。然后点File ->save as,在弹出的对话框中选择 “保存在” D:\lpm_rom,输入文件名Mif1,文件名后缀选择.mif,取消最下面一行的Create new project based on this file的选择框的对勾,点击保存完成。

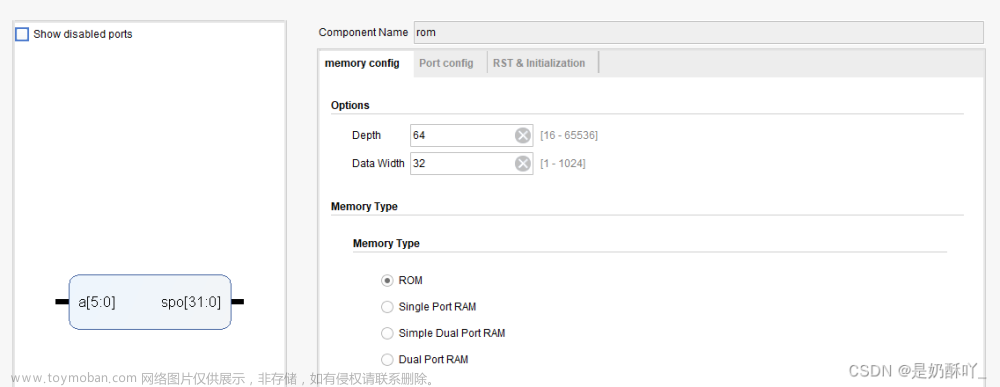

C.打开QuartusII,选File ->New Block Diagram/schematic File单击OK,进入图形输入界面,单击鼠标右键,点Insert ->Symobl…,在libraries库中选择需要的元件,(如果知道元件名称也可以直接输入),在这里我们在Name框中直接输入lpm_rom,点OK,在弹出的窗口中选择VHDL,在What name do you want for the output file? 点Browse,选择元件存放的文件夹D:\lpm_rom,给元件取名lpm_rom0,点击next ,进入LPM_ROM选择对话框,在currently select device family中选择芯片Cyclone III,选宽8位,64字节,选中Dual clock,点next进入下一界面, 去掉已打勾的“q”output port,然后点next进入下一界面,点browse,选前面已建立的D: D:\lpm_rom\ Mif1。mif文件,点next -> next,Finish完成lpm_rom0的输入。重复点鼠标右键选Insert Symobl…,在libraries库中择其他需要的input,output引脚。连接到lpm_rom0对应的端口,修改输入引脚名称一个为a[5…0],时钟名为clk, 输出引脚的名称为q[7…0],然后点save,在弹出的窗口Do you want to create a new project on this file? 回答“是”,点next -> next ,在窗口中选择存入新建的文件夹D:\lpm_rom中,项目名lpm_rom0,lpm_rom0,点next->next,在设备窗口中分别选择:Family为CycloneIII, package为PQFP, Pin count为240, Speed grade为8,点next -> next ->选择EP3C40Q248C8,Finish保存。

D.在快捷键中,点击编译键►完成编译。如果有错误,可返回前面重新检查、修改输入后再次编译,直到看到提示编译成功信息。

2.波形仿真:

A.打开QuartusII,选File File -> New other files -> Vector Waveform File,点击OK进入仿真界面。

B.在左空白处双击左键,在新出现的对话框的Radix中选择Hexadecimal(16进制),点Node Finder点list选中需要仿真的信号,a[5…0],clk,[7…0]点击OK->OK。

C.加入信号。

D.选仿真需要的时间,点击Edit,选择End time (100 us)。点a[0],设置为高电平。点clk (10 ns),一般可设置时钟的周期为10-100 us ,End time为1-100 us。

E.保存。系统会自动把后缀加上。

F.仿真。点快捷键 仿真。

3.引脚锁定

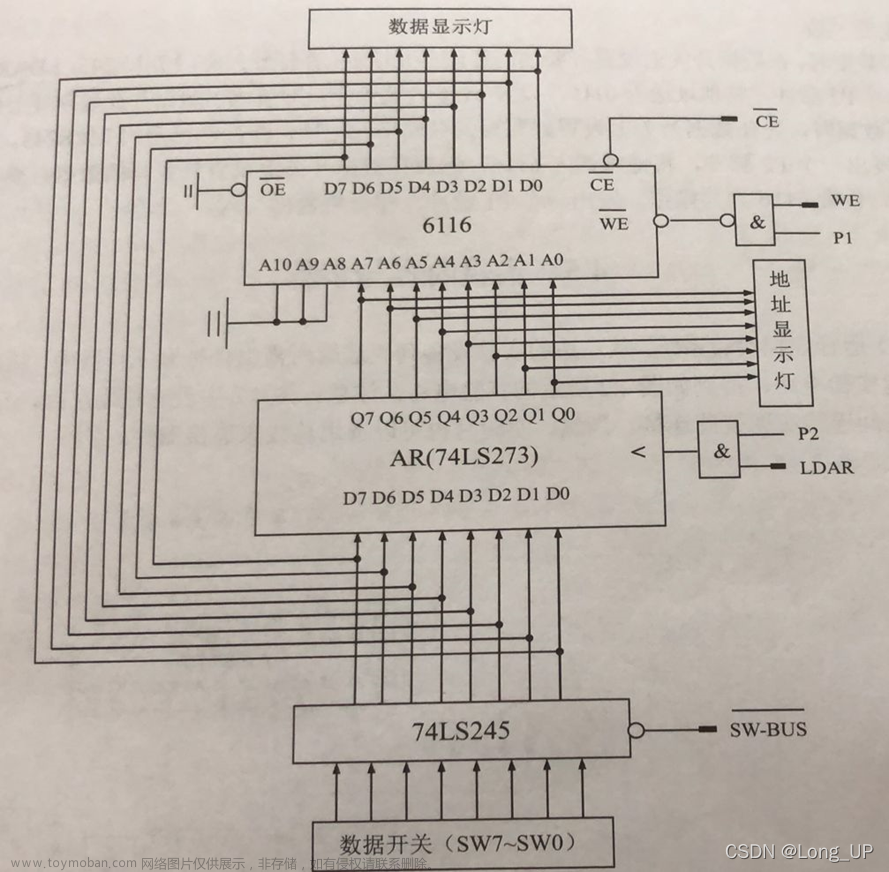

仿真完成后,选择菜单Assignments-> pins->Location,根据实验电路结构图NO。0和芯片引脚对照表, 查出a[5…0],clk,q[7…0] ,在核心芯片EP3C40Q240C8上所对应的引脚号,进行引脚锁定。引脚锁定后再次编译,点快捷键►编译。

4.下载

将电脑与实验箱通过并口连接接好,点快捷键,在出现的*.sof文件上, 选中program/configure点快捷键。即可设计下载到FPGA中。最后是用实验箱进行硬件测试。

四.实验要求

1.实验前认真复习LPM-ROM存储器部分的有关内容。

2.记录实验数据,写出实验报告,给出仿真波形图。

3.通过本实验,对FPGA中EAB构成的LPM-ROM存储器有何认识,有什么收获?文章来源:https://www.toymoban.com/news/detail-442908.html

五. 实验结果

1.存储器初始化文件内容:

2.LPM_ROM图形文件:

3.波形仿真结果:

4.引脚锁定结果:

5. 下载到FPGA:

6.FPGA实验板初始化状态:

选择实验电路模式为NO。0,24位数据输出由数码8至数码3显示,6位地址由键2、键1输入,键1负责低4位,地址锁存时钟CLK由键8控制,每一次上升沿,将地址锁入,数码管8/7/6/5/4/3将显示ROM中输出的数据。发光管8至1显示输入的6位地址值。

例如:当由键2、键1输入的地址为000001时,数码管3显示000001F,表示读取的数据为十进制的1;当由键2、键1输入的地址为010001时,数码管3显示000011FF,表示读取的数据为十进制的17。由此可见,本次实验成功地验证了FPGA中mega_lpm_ROM的功能。

六.思考题

1.如何在图形编辑窗口中设计LPM-ROM存储器?怎样设计地址宽度和数据线的宽度?

答:进入图形输入界面,双击鼠标左键,在Name框中输入lpm_rom,点OK,在弹出的窗口中选择VHDL,在What name do you want for the output file?中点Browse,选择元件存放的文件夹D:\lpm_rom,给元件取名lpm_rom0,点击next,进入LPM_ROM选择对话框,在currently select device family 中选择芯片Cyclone III,选宽8位,64字节。

2.怎样导入LPM-ROM的设计参数文件和存储LPM-ROM的设计参数文件?

答:点next进入下一界面,去掉已打勾的“q”output port,点next进入下一界面,点browse,选前面已建立的D: D:\lpm_rom\ Mif1。mif文件,点next->next,最后点击Finish完成lpm_rom0的输入。

3.怎样对LPM-ROM的设计参数文件进行软件仿真测试?

答:选File File->New other files->Vector Waveform File,点击OK进入仿真界面。在左空白处双击左键,在新出现的对话框的Radix中选择Hexadecimal(16进制),点Node Finder点list选中需要仿真的信号:a[5…0],clk,[7…0]点击OK。加入信号,选仿真需要的时间,点击Edit,设置End time为100 us。设置A组信号的变化为从0-63(十进制),每隔10us变化一次,同时设置时钟的周期为20us。保存,点快捷键 仿真。

4.怎样在实验台上对LPM-ROM进行测试?

答:仿真完成后,选择菜单Assignments->pins->Location,根据实验电路结构图NO。0和芯片引脚对照表,查出a[5…0],clk,q[7…0],在核心芯片EP3C40Q240C8上所对应的引脚号,进行引脚锁定。引脚锁定后再次编译,点快捷键►编译。将电脑与实验箱通过并口连接接好,点快捷键,在出现的*.sof文件中选中program/configure点快捷键即可将设计下载到FPGA中,最后用实验箱进行硬件测试。

七.心得体会

1.本次实验是这学期计组实验的第一次实验。通过本次实验,我初步掌握了FPGA中lpm_ROM的设置,复习了课本中只读存储器ROM的工作特性。

2.通过本次实验,我学会了用文本编辑器编辑mif文件配置ROM,将代码以mif格式文件加载于lpm_ROM中;

3.通过本次实验,我学会了如何将配置文件下载到FPGA中并进行硬件验证。

4.虽然实验中遇到了很多困难,如电路图少连了线、引脚分配错误、USB-Blaster数据线有问题,板子内部原因等等,但最终仍在老师的指导下成功完成了实验。文章来源地址https://www.toymoban.com/news/detail-442908.html

到了这里,关于西电计组实验一 存储器实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!