器件基础

芯片(chip):半导体材料制成的电路器件;

引脚(lead):半导体器件和外部连接的部分,排布在芯片两侧或四周

封装(packaging):将半导体器件以特定方式、特定材料包装起来,提高可靠性、便于使用;

数据手册(datasheet):芯片制造商提供的关于产品信息的文档,说明了芯片的功能

印制电路板(printed circuit board,PCB):薄的纤维玻璃板,印有铜线来连接元器件;

原理图(schematic diagram):表示电路的主要部分及元件之间的连接

思考:从器件的封装,延伸如何用器件构造系统?

如何用其设计系统?需要哪些组件和技术?

电器特性、引脚功能、接口形式、使用方法。

核心思想:硬件设计与软件设计、搭积木

共性方法:部件库(积木部件/元件库/函数库) + 逻辑组装 + 设计工具

基本电路术语与符号

接地电压/低电平:0V电压;

接地引脚(GND):接到一直时低电平的信号;

集电极电压/高电平:3V、5V、12V电压

任何时候,电路中的信号要么高要么低

电路供电电压Vcc、芯片工作电压Vdd、发射极电源电压Vee、编程电压Vpp

TTL电平:TTL器件+5V,高电平为逻辑“1”,低电平为逻辑“0”;

输出L: < 0.8V; H:> 2.4V;

输入L: < 1.2V; H: > 2.0V;

CMOS电平:CMOS器件12V,高电平为逻辑“1”,低电平为逻辑“0”;

输出L: < 0.1Vcc; H: > 0.9Vcc;

输入L: < 0.3Vcc; H: > 0.7Vcc;

RS-232电平:负逻辑电平,即负电平 -3到-12V为逻辑“1”,正电平+3到12V为逻辑“0”;

实际设计中,可以搭电路或采用专用器件进行不同电平的转换。

信号浮动

信号:是时-空域中,以特定载体(如光、电、声音等)和特定形式传输信息的能量单元;是信息的物理表示;

浮动信号(多驱动信号)

下图中如果没有任何输出信号,会有什么问题?

没有驱动,信号可能高也可能低,或者处于二者之间某个状态(浮动)——>依赖于信号两端元件的瞬时状态,无法预见;

下图中,如果任何一个选择信号都不是有效,会有什么问题?

信号浮动

如何解决:安装一个辅助元件来驱动其高低——>上拉电阻、下拉电阻;

三态门(三态缓冲器)

可以将信号驱动为高电压、低电压、浮动状态;

浮动状态即第三种输出状态,也称三态、高阻抗态;此时既不像输出0状态那样允许电流灌入,也不象输出1状态那样向负载提供电流,处于悬浮状态

用于多个数据源共享一根(组)线路,驱动同一信号。

上下拉电阻

简介

上拉电阻(Pull-up resistor):连接在元件信号引脚和高电平之间的电阻,用于将引脚信号钳位在高电平,或在驱动能力不足时提供电流。

通常其值可在1千欧到100千欧之间,值越大输出电平的延迟越大;值越小,电流越大,上拉能力越强,但损耗越大:V✖I。

上拉电阻就是接电源正极,下拉电阻接负极或地。

作用

上拉电阻和下拉电阻二者共同的作用是:避免电压的“悬浮”,造成电路的不稳定。

上拉电阻:

1、概念:将一个不确定的信号,通过一个电阻与电源VCC相连,固定在高电平;

2、上拉是对器件注入电流,灌电流;

3、当一个接有上拉电阻的IO端口设置为输入状态时,它的常态为高电平。

下拉电阻:

1、 概念:将一个不确定的信号,通过一个电阻与地GND相连,固定在低电平;

2、下拉是从器件输出电流,拉电流;

3、当一个接有下拉电阻的IO端口设置为输入状态时,它的常态为低电平。

上拉是对器件注入电流,下拉是输出电流,弱强只是上拉电阻的阻值不同,没有什么严格区分,对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

基本元件与逻辑

三极管(Bip Transistor,双极性结型晶体管)

有三个极,三个极分别为N型与P型组成;

作为一种可变电流开关,能够基于输入电压控制输出电流;

晶体管是电流控制元件。

场效应管(Field Effect Transistor,FET场效应晶体管)

利用控制输入回路的电场效应来控制输出回路电流的半导体器件;

场效应管是电压控制器件。

集成电路中,二者都抽象为为开关,向上支持逻辑门设计。

OC/OD门(掌握原理,用途)

开放收集器(OC门,NPN型三极管)掌握原理、用途

输出装置,实际为NPN型三极管;即可驱动输出,也可以处在高低电压

不定状态;

多个这种输出连接到同一信号上,只要一个为低电压,该信号就变为低

电压; 解决了总线竞争问题;

如两个外设向CPU发出中断请求,

示例:NPN开放收集器输出的结构

示例:开放收集器7407工作原理

漏极开路(Open Drain,OD)

N-MOS场效应管,漏极浮空;

在I/O向栅极供电时导通并“漏”电流(吸收电流),输出低电平;

也可以支持多个开漏输出引脚的“线与”连接。

漏极开路输出需要接一个上拉电阻(上图中的R),可以利用改变上拉电源的电压,改变输出电平。上拉电阻是接在输出引脚和输出电压(上图中的Vcc)之间,可以获得高电平输出。当内部N沟道场效应管关闭的时候,上拉电阻R会把输出拉到高电平,此时场效应管的漏电流将非常的小。当内部N沟道场效应管导通的时候,它会把输出引脚拉到接近GND,此时的电流是根据欧姆定律计算的(I=Vcc/R)。

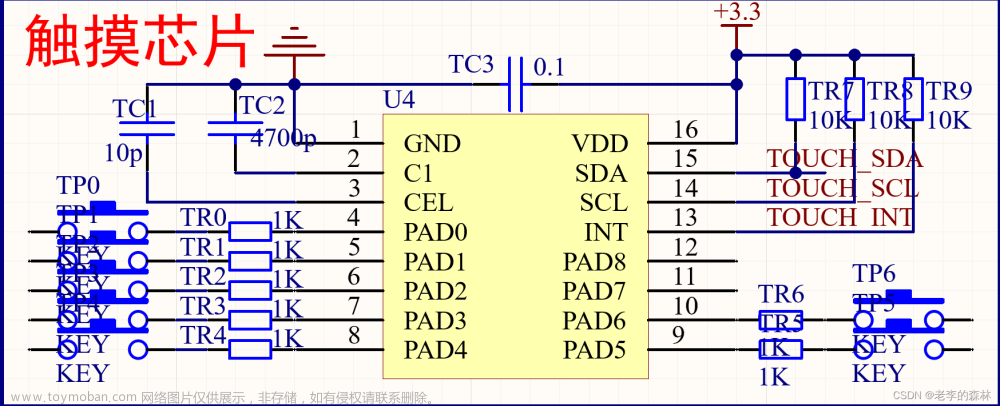

根据数据手册参数,R的值要大到足够限制电流小到不会伤害到N沟道场效应管。但不能太大,要比高阻抗状态小数量级以上的。同样的,Vcc也要在数据手册规定的范围内,比如说I²C的SDA双向串行数据传输引脚,漏极开路,需外接上拉电阻到Vcc(典型值10KΩ)。

集电极或者漏极开路输出引脚是由一个晶体管控制的,当晶体管关闭时,输出引脚为悬空状态(开路或者高阻态)。一个常见的列子就是当N沟道晶体管导通时,输出信号接地,但关断时,输出信号接高电平。

漏级开路时场效应晶体管的漏级与输出端相连接。集电极开路则是指双极型晶体管的集电极与输出端相连接。当晶体管关闭时,输出信号被上拉电阻拉高或者拉低。上拉电阻提供了一个未知的悬空状态。

推挽电路

常使用一对参数相同的功率三极管或MOSFET管,以推挽方式存在于电路中;

由图采用了两个互补的增强型MOSFET,顶部是P-MOS场效应管(Top-Transistor),底部是N-MOS场效应管

(Bottom-Transistor)。

多个OC型推挽电路不能进行“线与”型的逻辑操作,一条总线上只能有一个推挽输出器件,为什么?

两个OC输出同时驱动一个信号时,若驱动不一致则可能导致元件被烧坏,乃至系统瘫痪;这个问题是由电路设计错误造成的。

退耦与旁路

退耦(去耦)

1、电路网络中存在:感应产生的寄生电流或供电电路中形成的反冲电流;

2、当芯片改变输出端的电压时需要大量的电量改变输出信号,此时芯片供电电路电压会急剧下降,可能导致芯片停止工作;

如何解决?

退耦,其目的就是消除电路之间的寄生耦合;

电容具有滤波和电量存储作用;

平常情况下,电容充电;当电路突然需要大量电量时,电容放电;

退耦电容用于退耦,基于滤波作用消除电路回波噪声,或者基于储能来快速提供能量补充;

布防在信号输出银角,将输出信号的干扰作为滤除对象;

一般分布在电路板上离可能 需要大量电量的电路部分很近的地方;

最好不采用电解电容,电解电容是两层薄膜卷成的结构,这种结构在高频时表现为电感。

退耦电容的摆放原则:靠近电源的管脚,并且电容的电源走线和地线所包围的面积最小。

电路原理图中的退耦电容通常都集中表示,主要表明该类电容的数量

旁路电容

1、在电路中也是用于滤波、抗干扰的作用;

2、主要将输入信号中的高频噪声作为滤除对象,利用电容的频率阻抗特性,将前级携带的高频杂波滤除。文章来源:https://www.toymoban.com/news/detail-443816.html

驱动过载

元件的输出驱动能力有限,当一个输出对应过多元件的输入时可能导致驱动过载;

制造商已标明元件输出信号上的驱动电流以及所需的输入电流;

当出现驱动过载现象时需要增加驱动器电路;文章来源地址https://www.toymoban.com/news/detail-443816.html

到了这里,关于嵌入式电路基础的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!