前言:结合之前学习的基本门电路、逻辑电路的分析与设计,去剖析解编码器、译码器、数据选择器、加法器、数值比较器的模块设计与应用。

目录

一、编码器

1、工作原理

2、编码器-74LS148分析

3、应用74LS148接成16线—4线优先编码器

二、译码器

1、译码器定义

2、74145译码器分析

3、下面通过一个具体例子说明一用74145选择驱动指示灯和继电器的电路的方法。

三、数据选择器

1、数据选择器定义

2、数据选择器74LS153剖析

3、数据选择器74LS153-通道顺序选择电路

四、加法器

1、加法器定义

2、半加器分析

3、全加器分析

4、全加器电路

五、数值比较器

1、数值比较器定义

2、数值比较器逻辑图

一、编码器

1、工作原理

为了区分不同的事物,将其中的每个事物用一个二值代码表示,即编码。在二值逻辑电路中,信号都是以高、低电平的形式给出的。因此,编码器的逻辑功能就是把输入的每一个高、低电平信号编成一个对应的二进制代码。

目前经常使用的编码器有普通编码器和优先编码器两类。在普通编码器中,任何时刻只允许排了队,当几个输入信号同时出现时,只对其中优先输入一个编码信号,否则输出将发生混乱。在优先编码器电路中,允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序权最高的一个进行编码。

2、编码器-74LS148分析

编码器-74LS148:本例采用了74LS148优先编码器-括号中的符号为实际芯片中的符号。

V18(S1):代表使能

Y0-Y7:代表8路输入,其中Y7优先级最高

A0-A2:代表3路输出

E0(S0):代表输出,已有的编码

GS(Gs):代表输出,没有的编码(扩展的编码)

设计优先编码器时已经将所有的输入信号按优先顺序权最高的一个进行编码。图中当S1信号使能的时候,输出均是1。当Y0-Y7信号输入1的时候,扩展编码输出1.。其余按顺序,输出000-111。

3、应用74LS148接成16线—4线优先编码器

下面通过一个具体例子说明一利用SO、GS信号实现电路功能扩展的方法。

左边芯片代表优先级高的,右边芯片代表优先级低的。通过左边的状态输出引脚E0(S0)控制右边输入引脚Ei上面,低电平有效。并通过Gs脚区分当前芯片是否使能,驱动左边的高位,再通过右边的芯片控制其他3位,最终实现4个二极管的编码。

后期补充multisim源文件演示。

二、译码器

1、译码器定义

译码是编码的逆过程,把二进制码还原成给定的信息符号(数符、字符或运算符等)。能完成译码功能的电路叫译码器。译码器输入二进制数码的位数n与输出端数m之间的关系为m<=2^n。若m=2^n称为全译码。m<2^n称为非全译码。

译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。

2、74145译码器分析

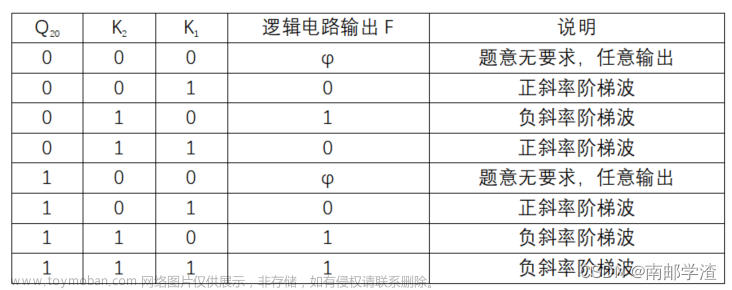

74145是BCD码到十进制数译码器,其逻辑功能见表,其中×为随意态。74145为集电极开路输出型的电路.其吸收大电流的能力较强且输出管具有高的击穿电压。

观察真值表,译码是往右下角连线的规律。

3、下面通过一个具体例子说明一用74145选择驱动指示灯和继电器的电路的方法。

左边是自发生器,采用16进制从0000000-00000009滚动发射。led不停轮回显示。

三、数据选择器

1、数据选择器定义

数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关,如图所示,图中有四路数据DO~D3,通过选择控制信号A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q。

2、数据选择器74LS153剖析

真值表

S代表使能,1代表无效,0代表有效

选择D0-D3输出到Q

2和14脚控制信号输入,7脚控制输出

3、数据选择器74LS153-通道顺序选择电路

用数据选择器74153(双4选1)和J-K触发器7470组成的4通道顺序选择器电路触发器组成的计数器对时钟脉冲CP计数,周而复使地进行00到11的计数,其输出使74153顺序将1D0~1D3选中,输出端7脚依次按位得到数据输出ID0~ID3,1CLR端可对计数器清零。

当我们的灯阶段0的时候会亮,接到123的时候会灭

函数发生器的设置为10Hz,通过频率计分析,灯泡亮灭的频率是2.5hz,正好是1/4。

函数发生器的设置为10Hz,通过频率计分析,灯泡亮灭的频率是2.5hz,正好是1/4。

四、加法器

1、加法器定义

两个二进制数之间的算术运算无论是加、减、乘、除,目前在数字计算机中都是化做若干步加法运算进行的。因此,加法器是构成算术运算器的基本单元。

如果不考虑有来自低位的进位将两个1位二进制数相加,称为半加。实现半加运算的电路叫做半加器。

全加器是一种广义名称.就其电路结构而言,它是一种二进制运算的单元电路。从器件角度看,它又是一种最基本的二进制算术运算器件。实际的加法运算,必须同时考虑由低位来的进位,这种由被加数、加数和一个来自低位的进位数三者相加的运算称为全加运算。执行这种运算的器件称为全加器。

2、半加器分析

AB是输入

S是输出。例如1 与1相加,S值为0

C是代表进位状态

3、全加器分析

CBA代表三个输入

S代表结果,当11、111的时候,S等于0,需要进位

C代表进位,当010、100、001、000的时候,C是0,当需要进位的时候C输出1

4、全加器电路

下面通过一个具体例子说明一全加器电路设计方法。

先介绍一下逻辑变换器,ABCEFGH代表输入,右边代表输出。

逻辑转换器提供六种转换功能︰门电路转换为真值表、真值表转换为逻辑表达式、真值表转换为最简逻辑表达式、逻辑表达式转换为真值表、逻辑表达式转换为门电路、逻辑表达式转换为与非门电路。

逻辑转换器的ABC输入端,连接到了A、B、C0的输入端,输出端连接到C进位的输出端。

五、数值比较器

1、数值比较器定义

在一些数字系统(例如数字计算机)当中经常要求比较两个数字的大小。为完成这一功能所设计的各种逻辑电路统称为数值比较器。

首先讨论两个1位二进制数A和B相比较的情况。这时有三种可能:

(1)A>B(即A=1、B=0),则=1,故可以用﹑―作为A>B的输出信号Y(A>B)。

(2)A<B(即A=0、B=1),则 =1,故可以用︰作为A<B的输出信号Y(A<B)。

(3)A=B,则A⊙B=1,故可以用A⊙B作为A=B的输出信号Y(A-B)。

⊙代表同或

2、数值比较器逻辑图

将以上的逻辑关系画成逻辑图,即得图:

文章来源:https://www.toymoban.com/news/detail-444149.html

文章来源:https://www.toymoban.com/news/detail-444149.html

分析 AB代表输入,先相与,再同或,实现了比较数值比较器。文章来源地址https://www.toymoban.com/news/detail-444149.html

到了这里,关于数字电路和模拟电路-6组合逻辑模块及其应用(上)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!