一、开发流程

二、新建文件夹(不许出现中文路径)

先创建一个工程文件夹flow_led再创建四个子文件夹

doc存放工程的设计文档或者其他一些datasheet文档、数据手册

par存放工程文件

rtl存放设计文件,也就代码

sim存放工程的仿真文件

第一个第四个可以为空,但是做此可以有良好的习惯

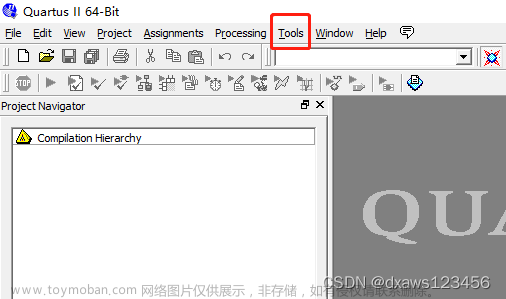

三、新建工程

这是打开一个工程向导

这是选择FPGA的芯片型号的

选择第三方EDA的工具的

最后的信息确认

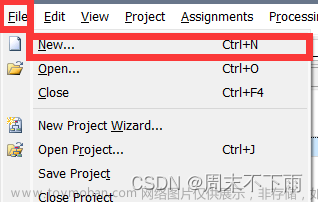

三、添加设计文件

选择Verilog语言进行编写

四、配置工程

咳咳上面应该才是配置工程,三和四写反了

找一个流水灯的代码

module flow_led(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output reg [3:0] led //4个LED灯

);

//reg define

reg [23:0] counter;

//*****************************************************

//** main code

//*****************************************************

//计数器对系统时钟计数,计时0.2秒

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24'd0;

else if (counter < 24'd1000_0000)

counter <= counter + 1'b1;

else

counter <= 24'd0;

end

//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd1000_0000)

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

end

endmodule

ctrl+s保存到rtl文件夹下

五、分析与综合

六、分配引脚

点击的是…/rtl/flow_led.v这个代码页面

这个东西只需要设置一次就够了

将复用引脚改成普通的IO

咳咳,接下来才是真正的分配引脚

打开引脚分配表

对照着填入就行

有点乱,被我弄得,不过将就着看吧,点击关闭就行

刚刚设置的引脚都在qsf这个文件里面,如果想要更改,可以直接在这个文件里面更改

七、编译工程

这里是进度:

分析与综合

布局布线

生成用于加载程序的文件

时序分析

EDA网标

看到警告不要慌(我当时是慌了),其实好像是时序没做仿真没做的原因

八、下载程序

点击programmer

添加驱动

添加下载文件

下载程序

嗯,超级紧张,害怕出现问题

成功了!!!

贼开心啊

注意点:如果关闭后,再次打开电源,是不会进行流水灯的

因为默认是保存在片内SRAM的,而这个是掉电不保存的。如果想要掉电保存的话,需要固化到开发板的Flash中

而固化文件是jic文件,需要手动将sof文件变成jic文件

附、修改成jic文件

jic文件比sof文件时间长,并且掉电再上电才有结果

如果想擦除程序

如果想再写入,在前面打勾就行

点灯小视频文章来源:https://www.toymoban.com/news/detail-444868.html

点灯了点灯了文章来源地址https://www.toymoban.com/news/detail-444868.html

到了这里,关于FPGA新起点V1开发板(三)——Quartus II软件的使用(流水灯的烧录以及sof转jic的方法记录)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!