1.复位概述

复位最基本的作用是使得电路进入一个我们预知的状态。主要使用有:

-

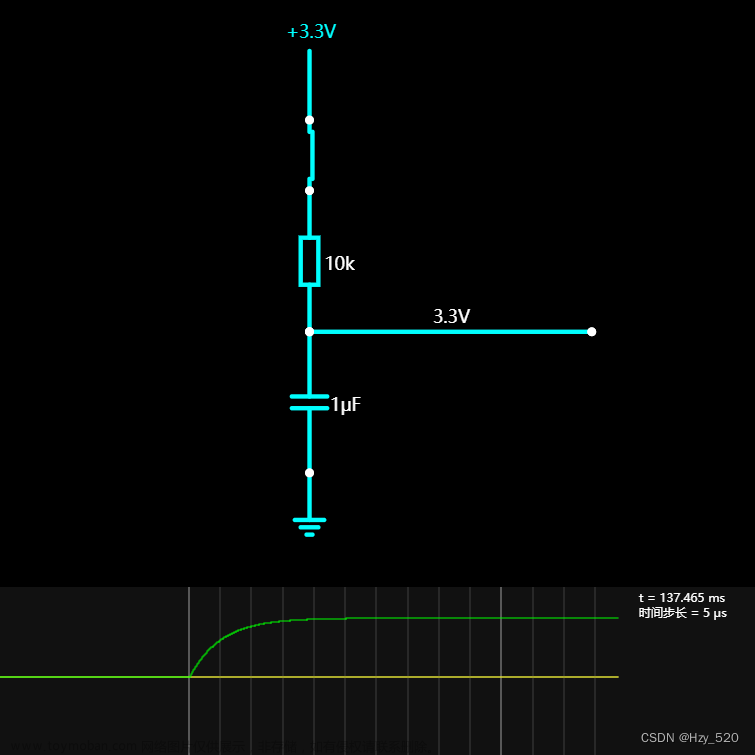

电路上电复位;

电路在上电前处于一个未知的不确定的状态,所以我们需要进行一次复位,使得进入我们可以确定的状态后进行后续的工作; -

电路错误状态复位;

电路进入错误状态后(如状态机跑飞了,系统供电炸了等),我们需要电路可以回到可以控制的状态,这时候我们就会进复位;

复位信号在数字电路里面的重要性仅次于时钟,对电路的复位,就是针对于寄存器的复位,毕竟电路中的值都是由寄存器提供。大部分的寄存器需要复位信号,但也有少数寄存器没有复位信号。

2.同步复位与异步复位

1.同步复位

同步复位指的时,复位肯定发生在时钟的上升沿,也就是复位是与时钟同步的,如下代码:

module DFFsync(q,ck,r,d);

input ck,d,rst;

output q;

reg q;

always @(posedge ck)begin //这里没有复位的下降沿触发

if(~r) q <= 0;

else q <= d;

end

endmodule

2.异步复位

异步复位:只要复位信号进行相应的跳变则进行复位,即触发信号加入时钟的相应跳变,复位不在需要时钟边沿进行触发;

如下异步复位代码:

module DFFsync(q,ck,r,d);

input ck,d,rst;

output q;

reg q;

always @(posedge ck or negedge r)begin //这里加入了or选项

if(~r) q <= 0;

else q <= d;

end

endmodule

3.同步复位优缺点

优点如下:

- 抗干扰能力强,可以剔除复位信号毛刺;

- 有利于静态时序分析工具;

- 有利于基于周期的仿真工具的仿真;

缺点如下:

- 占用更多的逻辑资源;

- 对复位信号脉宽有要求,太窄的脉宽识别不到,必须大于时钟周期;

- 依赖于时钟,若时钟出问题,则也复位不了;

4.异步复位优缺点

优点如下:

- 无需额外的逻辑资源,实现简单;

- 有特定的布线资源,保证复位管脚到寄存器的时钟偏差最小;

- 复位不依赖时钟,时钟出问题了还是可以复位;

缺点如下:

- 复位信号 敏感,若出现毛刺,则会误复位;

- 复位信号的释放随机,可能导致时序违规(复位释放处于时钟沿附近,导致建立时间/保持时间不满足),使得电路进入亚稳态;

5.异步复位、同步释放

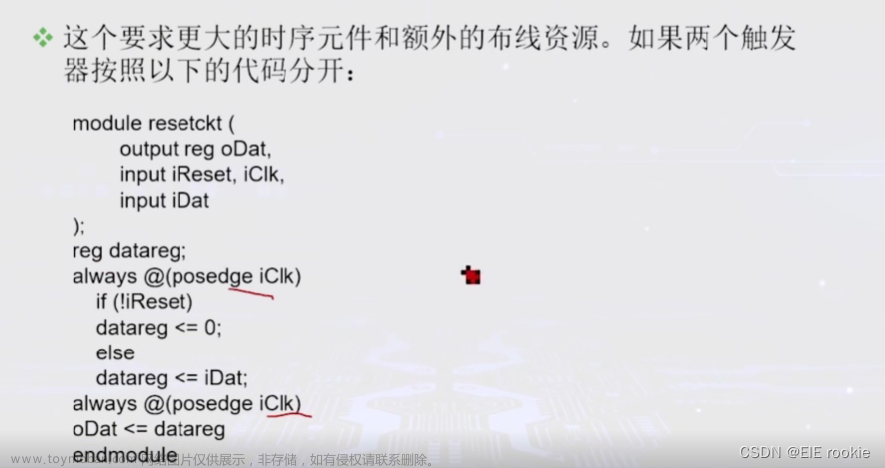

异步复位、同步释放整个的思路是,但复位信号有效是是立刻生效的,但复位信号的撤销需要遵从时钟沿;

如上图(参考别处的)我们进行一些分析;

- rst_async_n 生效 即(rst_async_n==1 -> rst_async_n==0)

此时1框内的寄存器是马上更新的,所以输出的rst_sync_n也是马上可以体现出来的,实现对2框内的电路进行异步复位; - rst_async_n 无效 即(rst_async_n==0 -> rst_async_n==1)

此时由于电路设计时,图上寄存器只对复位信号的下降沿敏感,所以当失效模式下,并不会马上更新,所以就算你的复位信号在1框中第一个寄存器的时钟沿进行变化,但是由于中间加了一个寄存器不会立马传到框2中去(这个寄存器就是拿来同步的);实现了同步释放;

此上就实现了异步复位,同步释放。简单代码实现如下;文章来源:https://www.toymoban.com/news/detail-446036.html

...

always @(posedge clk or negedge rstn_in)begin

if(~rstn_in)begin //实现异步复位

rstn_in_d1 <= 1'b0;

rstn_in_d2<= 1'b0;

end

else begin //实现同步释放

rstn_in_d1 <= rstn_in;

rstn_in_d2 <= rstn_in_d1;

end

end

assign rstn_out = rstn_in_d2;

...

异步复位、同步释放一般使用在不同时钟域复位信号传递,需要将复位信号同步到另一时钟域,使得复位在释放时确保满足寄存器时序要求;文章来源地址https://www.toymoban.com/news/detail-446036.html

6.关于异步复位、同步释放的思考

- 如果没有前面两级触发器的处理,异步信号直接驱动system模块,会出现什么情况?

答:可能出现时序违规,即复位信号的释放在时钟的跳变沿附近,导致建立时间/保持时间得不到满足; - 复位信号存在亚稳态,有危险么?

答:任何信号存在亚稳态都是有危险的,我们只能减小这个危险出现的概率,所以我们用了两级的触发器进行同步,就是为了减小这个亚稳态传播下去的概率,两级已经足够了,当然要三级也可以,但没必要,可以这么理解:一级不够,二级刚好,三级浪费;

到了这里,关于数字电路之复位的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!