概述

锁相环 (Phase-Locked Loop) 在现代电子与通信系统中, 扮演着至关重要的角色. 凭借其独特的同步和频率调整能力, 锁相环已成为实现高性能, 高稳定性系统的基石. 那边, 锁相环究竟是什么? 它是如何工作的? 又在哪些领域中发挥着关键作用呢? 小白我来带大家一探究竟.

什么是锁相环 (PPL)

锁相环是一种闭环反馈控制系统. 用于生成与输入信号同步且相位相同的输出信号. 它的核心功能是在输入信号的相位变化时, 自动调整输出信号以保持同步. 这使得锁相环成为了一种理想的频率和相位控制技术.

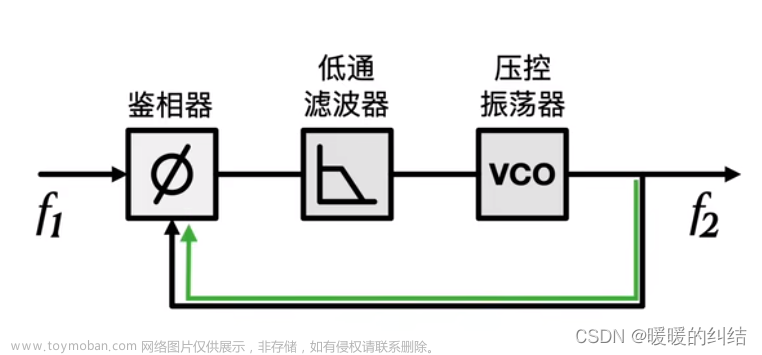

锁相环的基本组成

锁相环主要由以下几个部分组成:

- 相位比较器 (Phase Detector): 相位比较器负责比较输入信号和反馈信号的相位差, 并将其转换为电压信号

- 低通滤波器 (Low-Pass Filter): 低通滤波器对相位比较器的输出信号进行滤波, 以消除高频噪声和相位抖动

- 电压控制振荡器 (Voltage-Controlled Oscillator): 根据低通过滤波器的输出电压调整输出信号的频率和相位

- 反馈分频器 (Feedback Divider): 反馈分频器对 VCO 的输出信号进行分频处理, 并将其反馈给相位比较器

锁相环的工作原理

锁相环的工作原理可以分为以下几个步骤:

- 当输入信号和反馈信号的相位不同步时, 相位比较器检测到相位差, 并生成一个与相位差成正比的电压信号

- 低通过滤波器对电压信号进行滤波出来, 去除噪声和抖动

- 电压控制振荡器根据滤波后的电压信号调整输出信号的频率和相位, 使输出信号逐渐接近输入信号的相位

- 当输出信号与输入信号的相位达到同步时, 锁相环进入锁定状态, 系统维持稳定度相位同步

锁相环应用

锁相环在各种领域具有广泛的应用, 以下是一些主要的应用:

- 频率合成: 锁相环可以用于生成一定倍数的输入频率, 从而实现高精度的频率合成. 在无线电通信, 雷达和导航系统中, 频率合成器是关键组件之一

- 时钟恢复: 在数字系统通信中, 锁相环可以从接受到的数据信号中恢复时钟信号, 从而实现时钟同步. 这对于高速数据传输和串行通信协议 (如 USB, PCI Express 和 SATA 等) 至关重要

- 频率和相位调制: 锁相环可以用于实现频率调制 (FM) 和相位调制 (PM), 这些都是无线通信中常用的调制方式. 通过控制 VCO 的输入电压, 可以实现信号的调制和解调

- 频偏补偿: 锁相环可以用于补偿频率源和飘逸, 从而实现高稳定性的时钟信号. 在卫星通信, 全球定位系统 (GPS) 和高精度测量仪器中, 频偏补偿功能至关重要

- 告诉数据转换: 在告诉数据采集和信号处理应用中, 锁相环可以用于生成精确的采样时钟, 从而实现高性能的模块转换 (ADC) 和数模转换 (DAC)

- 电源管理: 在开关电源和电压调节器中, 锁相环可以用于控制开关频率, 以实现高效的电源转换和稳定的输出电压

STM32 中锁相环的应用

在 STM32 中, 锁相环主有以下作用:

- 系统时钟生成: STM32 通常使用锁相环从外部晶振或内部时钟源生成所需的洗头工时钟. 例如: 通过使用 PLL, 可以将外部 8 MHz 晶振提升到 72 MHz 或更高, 以满足高性能应用的需求

- USB 时钟生成: 在具有 USB 功能的 STM32 微控制器中, 锁相环可以用于生成精确的 48 MHz 时钟, 以满足 USB 2.0 全速 (12 Mbps) 或高速 (480 Mbps) 通信的要求

- 音频时钟生成: 在音频处理器应用中, STM32 微控制器的锁相环可以用于生成特定的硬盘采样率 (如 44.1 kHz, 48 kHz 等) 以及 I2S 和 SPDIF 接口所需的位时钟和帧时钟

- ADC 和 DAC 时钟生成: 在高速数据采集和信号处理应用中, 所喜爱你该换可以用于为 ADC 和 DAC 提供精确的采样时钟, 从而实现高性能的数据转换

文章来源:https://www.toymoban.com/news/detail-446395.html

文章来源:https://www.toymoban.com/news/detail-446395.html

STM32 配置锁相环

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

// 配置外部晶振作为HSE时钟源

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

// 根据外部晶振频率和所需系统时钟频率设置PLL参数

// 这里假设外部晶振为8 MHz,目标系统时钟频率为72 MHz

RCC_OscInitStruct.PLL.PLLMUL = RCC_PLL_MUL

}

总结

锁相环在电子和通信领域具有广泛的应用, 它为实现高精度的时钟信号提供了重要支持. 我们简单介绍了锁相环的基本原理, 工作方式和应用, 希望能给大家提供一个全面的了解.文章来源地址https://www.toymoban.com/news/detail-446395.html

到了这里,关于【STM32】知识补充 锁相环原理与应用解析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!