总述

在这一次实验里,我学习了电路模拟的基本办法,具体而言是virtuoso和hspice,还有custom waveform软件基本功能的使用,达到了通过电路模拟验证延迟,验证功耗,验证逻辑功能的目的。

反相器的设计:

反相器是可以将输入信号的相位反转180度的电路元件,可以用很多种方法实现。参考教材:

采用最右侧的CMOS反相器结构,在virtuoso里新建lib和cellview,通过引入其它库里的nmos和pmos进行绘制。

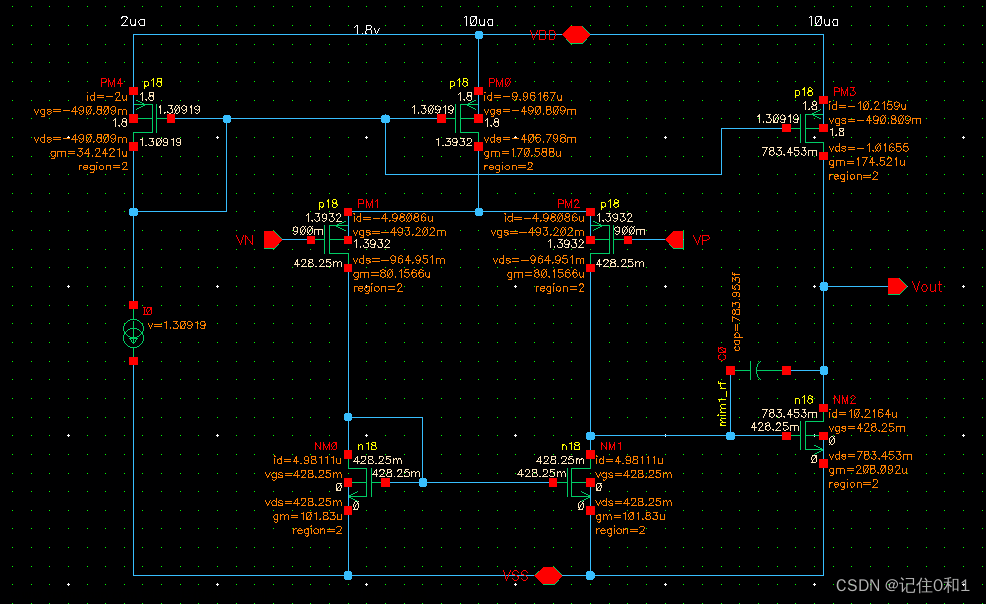

反相器电路图:

随后导出反相器的网表并加以激励信号等进行仿真,得到效果图如下所示。验证了反相器的功能。

三输入异或门:

由与非门构成。与非门由以下电路组成:二输入与非门构成二输入异或门,进一步构成三输入异或门。

对电路导出网表进行仿真,得到结果如下,基本验证了其三输入异或功能。

三输入与非门:

为译码器做铺垫。

结论:该三输入与非门功能完备,可以作为子器件在译码器电路中使用。

2-4译码器:

电路图:

由与非门和反相器组成,这两个元器件在之前已经创建、调试完毕,可以直接使用。

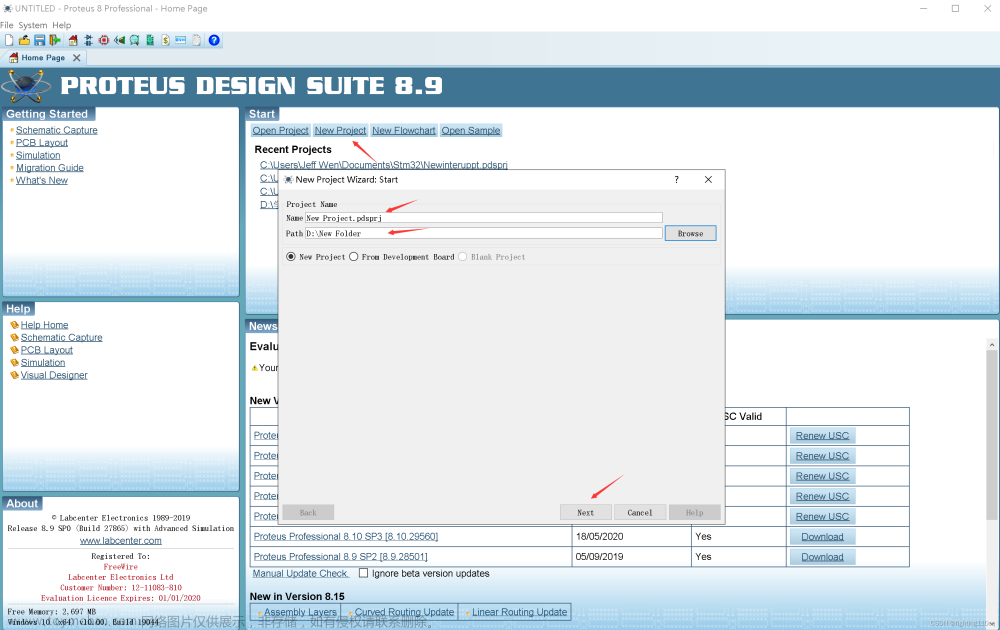

编写网表后:

功能验证

由spice中模拟电压输入语句对应以上输出波形可以看出,该元件顺利发挥了2-4译码器的功用,是正确的。

custom waveform的作用类似于示波器,可以观察波形并调用测量工具获得想知道的信息。

延迟时间

为了方便测定,自定义输入的电压信号从0.2开始到4.8为最高,此时以2.5为50%处。

上升延迟时间:输出信号下降到V50%的时间减去输入信号上升到V50%的时间,记为tpLH;

下降延迟时间:输出信号上升到V50%的时间减去输入信号下降到V50%的时间,记为tpHL。

综合使用measurement tools和光标进行测量。

C等效=0.1pF时,单个Y0~Y3的电容仿真为0.025pF.

由图可见,仅改变A0/A1时,tpLH=155.0pm,tpHL=4.97pm

仅改变片选时,tpLH=147pm,tpHL=22.4pm

C=1pF时,单个Y0~Y3的电容仿真为0.25pF.

仅改变A0/A1时,tpLH= 431pm,tpHL=87.4 pm

仅改变片选时,tpLH=435pm,tpHL=52.7pm.

电路功率

通过在网表中加入以下语句实现平均功耗的计算:

运行仿真后由下图可知,当等效电容为0.1pF时平均功耗为727.0943uW, 1pF时平均功耗为1.8402mF。

文章来源:https://www.toymoban.com/news/detail-446530.html

文章来源:https://www.toymoban.com/news/detail-446530.html

实验总结

在本次实验中,我对硬件编程和学习的重要工具:模拟仿真有了较为深入的理解。在使用Virtuoso的过程中,我对硬件设计的“层次”有了更深一步的理解。譬如我的三输入异或和2-4译码器,前者并未采用子器件的方式进行设计,导致最后呈现出的是令人难以一眼看明白构造对应的功能的晶体管,想要修正问题也很麻烦;但反观译码器的电路图,由于引用了子器件而格外清晰明确,且更方便看出其功能,也便于调试。文章来源地址https://www.toymoban.com/news/detail-446530.html

到了这里,关于使用Virtuoso和hspice进行电路输入与模拟的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!