一、1位全加器设计

1、原理图输入方法设计1位全加器

(1)、半加器的设计

半加器: 指对输入的两个一位二进制数相加a与b,输出一个结果位sum和进位cout

半加器真值表:

| a | b | sum | cout |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

半加器输出表达式:

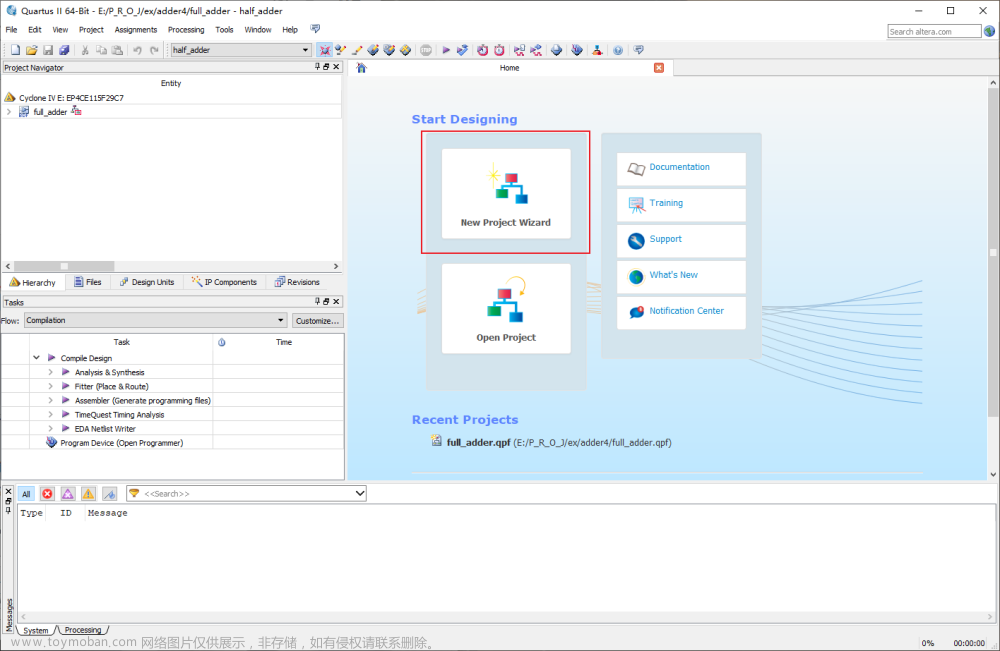

项目创建:

打开Quartus创建新项目:

设置项目路径及名称(adder4位实验名命名):

选择芯片(EP4CE115F29C7):

新建原理图文件:

点击File->New,然后选择Block Diagram/Schematic File:

选择元件and2和xor,并绘制原理图:

保存编译,将原理保存至adder4文件夹下,并命名为half_adder.bdf

此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

将项目设置为可调用元件:

半加器仿真:

创建一个向量波形文件,选择菜单项 File→New->VWF:

添加信号:

编辑信号:

保存文件并启动功能仿真:

通过仿真结果可以发现当a和b相同时s为0,否则为1;逻辑关系属于异或;当a和b同时为1时,co等于1,其余都为零,逻辑关系为与。

(2)、全加器的设计

全加器: 全加器是指对输入的两个二进制数相加(A与B)同时会输入一个低位传来的进位(Ci-1),得到和数(SUM)和进位(Ci);一位全加器可以处理低位进位,并输出本位加法进位。

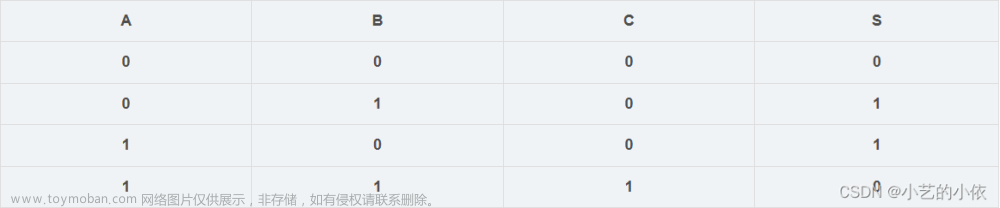

全加器真值表:

全加器输出表达式:

新建原理图文件:

点击File->New,然后选择Block Diagram/Schematic File,选择元件half_adder和or

2,并绘制原理图:

将原理保存至adder4文件夹下,并命名为full_adder.bdf:

将full_adder.bdf设置为顶层文件并编译:

此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

全加器仿真:

创建一个向量波形文件,并添加、编辑信号:

保存文件并启动功能仿真:

2、Verilog编程方法设计1位全加器

创建Verilog文件:

代码:

module full_adder2(

input ain,bin,cin,//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

output cout,sum//输出信号,cout表示向高位的进位,sum表示本位的相加和

);

assign sum=(ain^bin)^cin;//本位和输出表达式

assign cout=(ain&bin)|((ain^bin)&cin);//高位进位输出表达式

endmodule

保存并编译,此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

仿真实现:

创建一个向量波形文件,并添加、编辑信号:

保存文件并启动功能仿真:

3、上板检验

二、4位全加器设计

1、输入原理图方法设计4位全加器

4位全加器可看作4个1位全加器患行构成,具体连接方法如下图所示:

4位全加器输出表达式:

将full_adder设置为可调用元件:

新建原理图文件:

点击File->New,然后选择Block Diagram/Schematic File,选择元件full_adder,并绘制原理图:

将原理保存至adder4文件夹下,并命名为full_adder4.bdf,将full_adder4.bdf设置为顶层文件并编译:

此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

仿真:

创建一个向量波形文件,并添加、编辑信号:

保存文件并启动功能仿真:

2、Verilog编程方法设计4位全加器

代码:

module four (

num1,

num2,

cin,

cout,

sum

);

input [3:0] num1;

input [3:0] num2;

input cin;

output cout;

output [3:0] sum;

reg cout;

reg [3:0] sum;

reg add;

reg [1:0] cnt;

always @(num1 or num2 or cin)

begin

// 第一位

sum[0] = (num1[0] ^ num2[0]) ^ cin;

cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin);

add = cout;

// 第二位

sum[1] = (num1[1] ^ num2[1]) ^ add;

cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add);

add = cout;

// 第三位

sum[2] = (num1[2] ^ num2[2]) ^ add;

cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add);

add = cout;

// 第四位

sum[3] = (num1[3] ^ num2[3]) ^ add;

cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add);

add = cout;

end

endmodule

保存并编译,此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

使用modelsim进行验证:

验证代码:文章来源:https://www.toymoban.com/news/detail-446729.html

module four_tb ();

reg [3:0] num1;

reg [3:0] num2;

reg cin;

wire cout;

wire [3:0] sum;

four uut(

.num1(num1),

.num2(num2),

.cin (cin),

.cout(cout),

.sum (sum)

);

initial

begin

num1 <= 4'b0000; num2 <= 4'b0000; cin <= 0;

#10 num1 <= 4'b0000; num2 <= 4'b0000; cin <= 1;

#10 num1 <= 4'b0101; num2 <= 4'b0001; cin <= 0;

#10 num1 <= 4'b1000; num2 <= 4'b0100; cin <= 0;

#10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 0;

#10 num1 <= 4'b1100; num2 <= 4'b0100; cin <= 1;

#10 num1 <= 4'b0011; num2 <= 4'b0000; cin <= 1;

#10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 1;

end

endmodule

验证结果: 文章来源地址https://www.toymoban.com/news/detail-446729.html

文章来源地址https://www.toymoban.com/news/detail-446729.html

3、上板验证

到了这里,关于基于Quartus件完成1位全加器的设计及4位全加器的设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!