FPGA的第一课,学习Quartus编程运行仿真烧录的这一个流程,以一个十位的计数器为例。

芯片商家:ALTERA

编程软件:Quartus II

试验箱上的芯片型号:EP4CE6E22C8N

一、新建一个工程

打开软件后会会弹出一个窗口,点击【创建向导】

第一步:设置工程名和顶层硬件模块名

第二步:加入原先写好的文件,如若没有就直接点击下面的【next】即可

若要添加文件,则点击这个按钮

然后要记得点击【Add】不然添加进去的是一个只有文件名的空文件

第三步:根据试验箱上芯片的型号我选择【Cydone IV E】系列,设备型号【EP4CE6E22C8】。

第四步:选择仿真模式为【ModelSim】

第五步:列出来刚刚的选择,确认无误后,点击【Finish】

到此,就完成了工程的新建。

二、编写程序

1、新建一个【Verilog HDL File】文件

然后就开始码代码,以一个十位的计数器为例

三、编译

点击菜单栏中的三角形进行编译

若编译无误则会弹出如下提示:

1、可以查看所用到的资源:

2、如何看生成的电路

可以看到新建的电路如下:

文章来源:https://www.toymoban.com/news/detail-446749.html

文章来源:https://www.toymoban.com/news/detail-446749.html

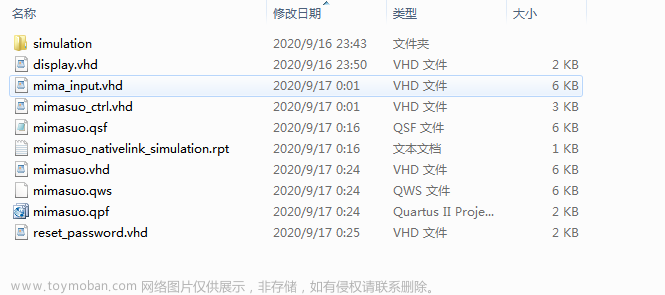

3、打开文件夹,可以看到需要烧录的文件

文章来源地址https://www.toymoban.com/news/detail-446749.html

文章来源地址https://www.toymoban.com/news/detail-446749.html

到了这里,关于【FPGA实验0】Quartus建立工程文件以及仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!