一丶什么是全加器

半加器比较容易理解,它的电路指对两个输入数据位(a、b)相加,输出一个结果位(sum)和进位(cout),但没有计算进位输入的加法器电路。

输出表达式

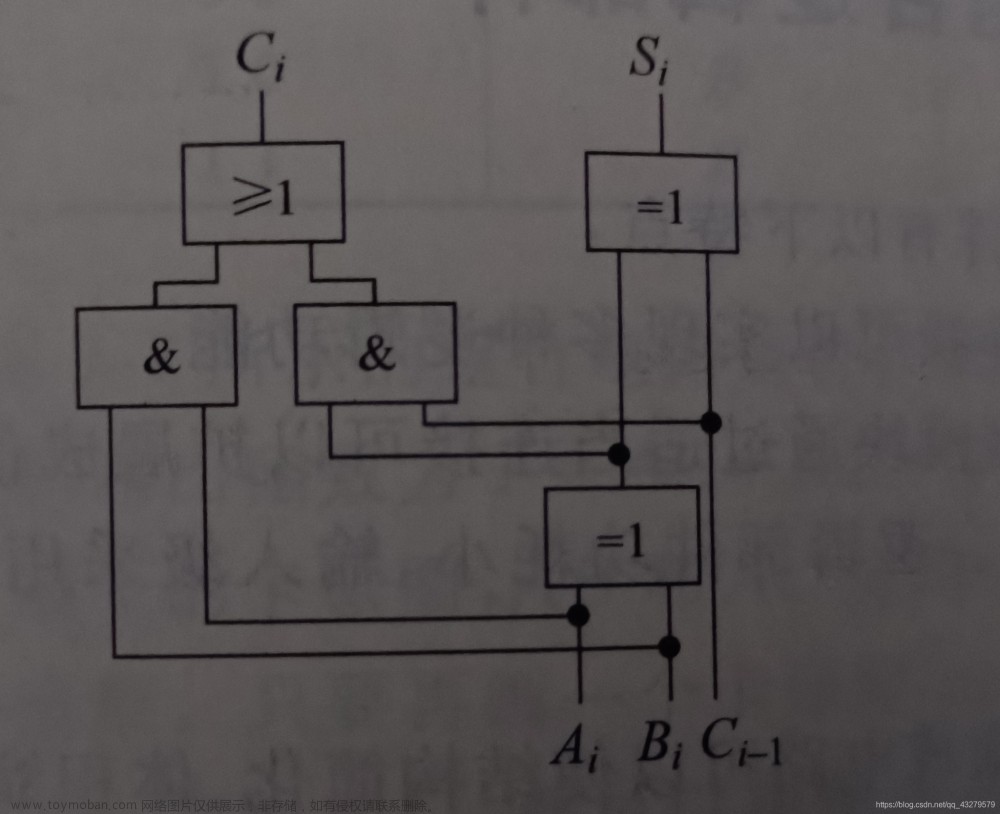

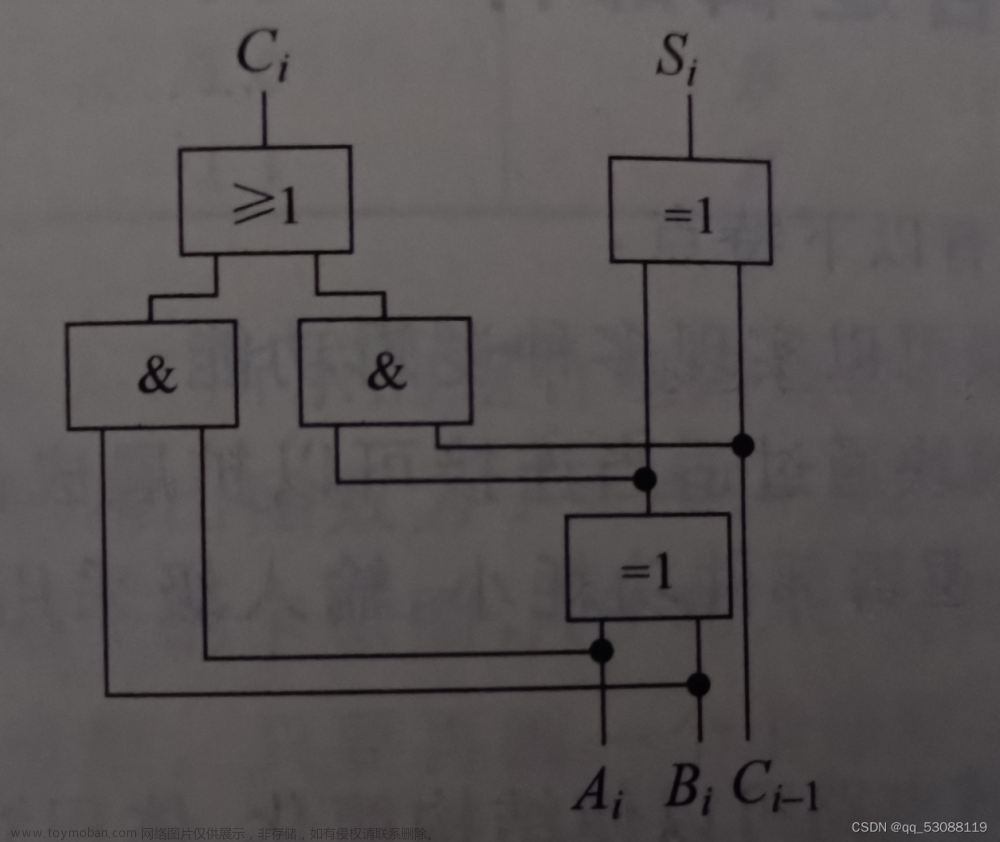

相比半加器,全加器是将低位进位输入也代入计算的加法电路,同样输出一个结果位和进位。1位全加器就是计算带进位输入的 1位二进制数的加法电路,多个一位全加器进行级联可以得到多位全加器。

这里我们来理解一下低位进位和本位加法进位

对照真值表:

一开始的运算Ci-1=0,因为之前的运算没有产生进位,直至Ai=Bi=1时产生进位。 即: 0+0输出结果Si=0,没有进位,所以Ci=0.

1+0输出结果Si=1,没有进位,所以Ci=0. 1+1,根据二进制运算法则,进位,Ci=1,进位后输出结果清零,Si=0

二丶1位全加器的Verilog实现

module full_add2

(

input a,

input b,

input cin,

output sum,

output cout

);

assign sum = a^b^cin;

assign cout = (a&b)|((a^b)&cin);

endmodule

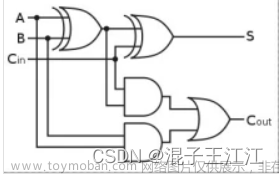

三丶深层解析sum及cout表达式的逻辑

对于代码中sum和cout的算式我们来进行分析:

首先考虑输出cout的逻辑表达式,什么条件下进位输出cout为1???分两种情况:

1、a和b相加已经产生进位。说明a和b都为1,此时不管cin是1还是0,不影响cout输出,这种情况对应逻辑表达式(a&b)

2、a和b相加没有产生进位。说明a和b都为0(此时不管cin是何值,进位输出cout都不会为1),或a、b其中一个为1,另一个为0,此时a与b不相同,用异或逻辑表示便是(a^b),这种条件下只有cin为1时,进位输出才为1,对应逻辑表达为(a ^b)&cin

总结1(cout):将上述两种情况加起来就是cout的逻辑表示,或逻辑表示加和,所以最终cout逻辑表达式为:cout = (a&b) | ((a^b)&cin)。

另外对于sum思考下,什么条件下sum输出逻辑1???sum由输入cin,被加数a,加数b,三者加和得到,若想结果sum为1,则cin,a,b三个数中,必然要有奇数个1(若有偶数个1,则二进制数加和,必会产生进位使得最低位sum为0)。

可以首先判断a,b是否相同,使用异或逻辑(a^b),然后分两种情况谈论:

1、a^b=1。说明a和b不相同,则必然一个为0,一个为1,此时已经存在一个1,那cin必须要为0才能使得sum为1,此时 (a ^b) 与cin相异,所以使用异或逻辑来描述这种情况 (a ^b) ^cin

2、a^b=0。说明a和b相同,同时为0或同时为1;此时不管哪种情况,cin必须要为1才能使得sum为1,此时 (a ^b) 与cin仍然相异,所以还使用异或逻辑来描述这种情况 (a ^b) ^cin

总结2(sum):综合上述两种情况,a ^b ^cin为sum的逻辑表达通式,用以计算a,b,cin中1的个数(奇偶),以此赋值sum是否为1。文章来源:https://www.toymoban.com/news/detail-447627.html

参考文章:https://blog.csdn.net/weixin_42294124/article/details/119853457文章来源地址https://www.toymoban.com/news/detail-447627.html

到了这里,关于【FPGA】如何理解全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!