一、生成DCP文件

1、在vivado-Tool-setting-project-setting-synthesis路径下,设置 -mode out_of_context(综合时不产生IO buffer)

2、将引脚约束注释掉,防止例化使用DCP文件时报错

3、将工程综合,打开综合设计。

4、在console输入命令,生成DCP文件:

write_checkpoint -key C:/Users/YDQ/Desktop/key_files.txt -encrypt top.dcp

其中-key C:/Users/YDQ/Desktop/key_files.txt -encrypt 为可选项,表示对目标工程按照key_files描述进行加密;

top.dcp为要生成的DCP文件名

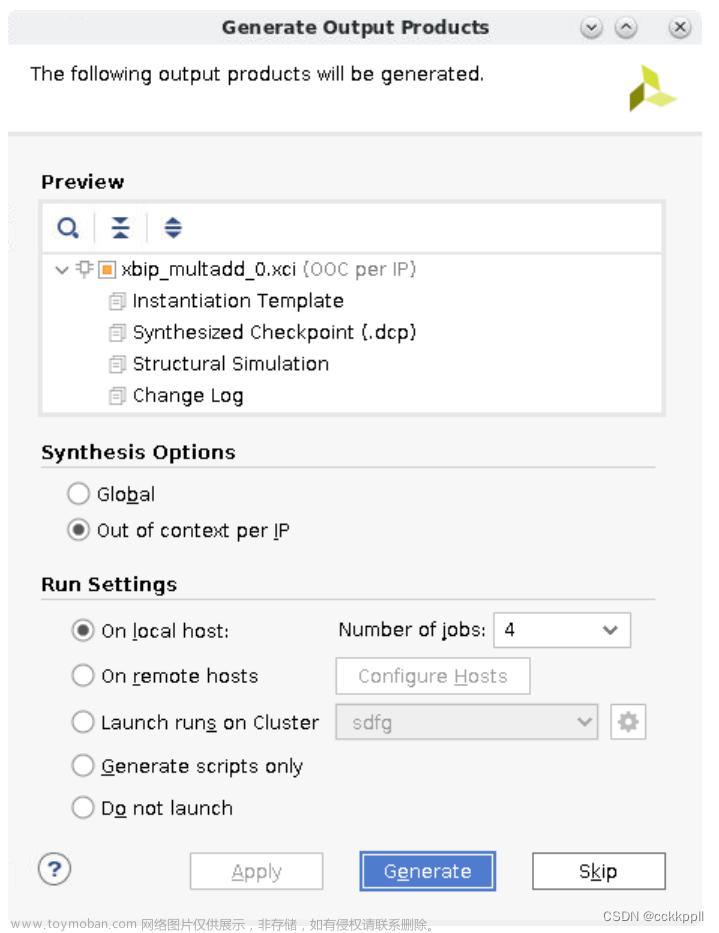

二、例化DCP文件

直接将top.dcp文件当作源文件加入到工程文件夹下,然后按照普通verilog或者VHDL文件进行例化即可。文章来源:https://www.toymoban.com/news/detail-447964.html

三、仿真含有DCP文件的工程

需要先将DCP文件转化为.v或者.vhd文件。操作步骤为:

1、使用cd [get_property directory [current_project]] 切换到工程路径下。或者使用CD命令到存放DCP文件的路径下也可。

2、open_checkpoint top.dcp。打开DCP文件。

3、在新打开的软件界面下输入指令:write_verilog -force -mode funcsim top.v

4、此时在DCP的路径下生成了top.v文件,将该仿真文件添加到工程中即可文章来源地址https://www.toymoban.com/news/detail-447964.html

到了这里,关于vivado中如何生成、例化和仿真DCP文件的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!