介绍

最近要考试了,所以我赶紧补习FPGA,我们用的是小梅哥的AC620开发板,软件是Quartus。推荐看这个视频教程:零基础轻松学习FPGA,小梅哥FPGA设计思想与验证方法视频教程

设计步骤

设计定义

用按键控制LED灯的亮灭就是一个二选一多路器,两个IO,a、b,可以是高电平,也可以是低电平。

输入按键按下时,

LED与a端口状态保持一致,

输入按键释放时,

LED与b端口状态保持一致。

创建工程

1.创建工程

2.添加文件

没有文件就不用添加了

3.选择器件型号

AC620的型号如下

4.设置仿真软件

5.新建Verilog文件

6.点此处新建

设计输入

module led_TEST(a,b,key_in,led_out);

module要和工程名称一致

a,b两个端口

key_in按键输入

led_out是led的输出

项目完整代码

module led_TEST(a,b,key_in,led_out);

input a;//输入端口a

input b;//输入端口b

input key_in;//按键输入,实现输入通道的选择

output led_out;//led控制端口

//当key_in == 0: led_out=a;按键按下是a端口

assign led_out = (key_in==0)? a:b;//假如key_in==0满足,led_out 就等于a,假如key_in==0不满足,led_out 就等于b

endmodule

开始验证

验证完成

进行testbench验证

再创建一个Verilog HDL文件作为testbench

`timescale 1ns/1ps

这里是仿真的量度和精度,1ns指以1ns为单位,1ps指可以精确到ps

testbench完整代码

`timescale 1ns/1ps

module led_test_tb;

//激励信号定义,对应连接到待测试模块的输入端口

reg signal_a;

reg signal_b;

reg signal_c;

// 待检测信号的定义,对应到待测试模块的输出端口

wire led;

//把他实例化进行连接,括号里面就是要连接的signal

led_TEST led_TEST0(

.a(signal_a),

.b(signal_b),

.key_in(signal_c),

.led_out(led)

);

//产生激励

initial begin

signal_a=0;signal_b=0;signal_c=0;

#100;//延时100ns

signal_a=0;signal_b=0;signal_c=1;

#100;

signal_a=0;signal_b=1;signal_c=0;

#100;

signal_a=0;signal_b=1;signal_c=1;

#100;

signal_a=1;signal_b=0;signal_c=0;

#100;

signal_a=1;signal_b=0;signal_c=1;

#100;

signal_a=1;signal_b=1;signal_c=0;

#100;

signal_a=1;signal_b=1;signal_c=1;

#200;

$stop;//停止仿真

end

endmodule

写完之后再进行验证

设置脚本

Assignments->Setting->Simulation

点最底下的Compile test bench

添加你的testbench

添加完成之后,就可以开始仿真了。

开始仿真

如果报错的话,要去设置一下仿真软件的路径:

Tools->Options

这里是你的Modelsim的路径,Modelsim-Altera也可以,选择你们安装的

再点击仿真

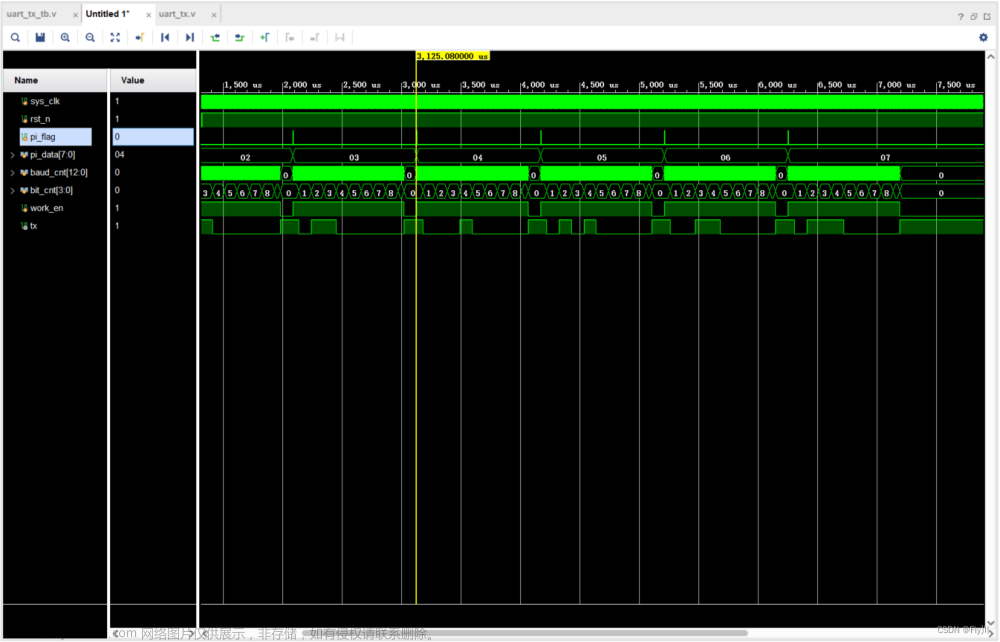

就出现了仿真波形

signal_c在低电平和a保持一致,signal_c高电平和b一致

布局布线

在功能仿真完成后,说明功能没有问题,那我们就可以全编译了

编译没问题后,可以开始门级仿真

后仿真

选择其在极限情况下的仿真

他有个很小的0.45ns的脉冲

引脚分配

Assignments->Pin Planner

根据板子的引脚表,我们给a和b分配的是GPIO

key_in用的M1

led_out用的L10

这个去查AC620的表就可以得到 文章来源:https://www.toymoban.com/news/detail-448459.html

文章来源:https://www.toymoban.com/news/detail-448459.html

下载程序

点击Programmer

右上角是Successful就成功了 文章来源地址https://www.toymoban.com/news/detail-448459.html

文章来源地址https://www.toymoban.com/news/detail-448459.html

到了这里,关于FPGA/Verilog HDL/AC620零基础入门学习——第一个项目按键控制LED的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!