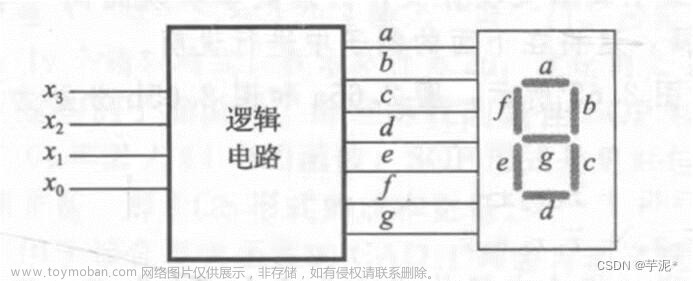

计数器同样由三个模块构成,分别为:顶层,计数器和译码器。

一、实验任务

大家这会儿数电理论课应该还没学到这里,所以对以上的部分名词进行解释:

1.异步清零(clr)

指不管现在时钟信号(clk)是什么,跑到哪儿了,只要你按下异步清零的按钮,计数器就应该马上归零。

2.同步使能(en)

其实就是一个计数器是否开始工作的开关,关闭了使能开关,计数器将会停在当前的计数值,不再随时间信号进行计数。

3.同步置数(load)

一个非常面向使用对象的功能。让使用者输入一个数值(预置数),再从这个数值进行加/减计数,因为是随着下一个时钟信号的到来才开始计数的,所以叫同步置数。

二、实验分析

输入信号:

clkin(时钟),clr(异步清零),upd(加减计数),en(使能开关),[3:0]data(预置数),load(同步置数)

输出信号:

seg0(位选),[3:0]Q(波形),[6:0]codeout (译码器),CO(进位信号)

三、代码

顶层文件:

module w_2495_03(codeout, Q, clkin, clr, CO, upd, en, load, seg0, data);

input clkin, clr, upd, en, load;

input [3:0] data;

output[6:0] codeout;

output [3:0] Q;

output CO,seg0;

w_2495_03_2(clkin, clr, Q, CO, upd, en, load, data );

w_2495_03_1 (codeout,Q,seg0);

endmodule译码器:

module w_2495_03_1 (codeout, Indec,seg0); //译码器

input[3:0] Indec;

output[6:0] codeout;

reg [6:0]codeout;

output seg0;

assign seg0 = 1;

always@(Indec)

begin

case(Indec)

4'd0 : codeout=7'b111_1110;

4'd1 : codeout=7'b011_0000;

4'd2 : codeout=7'b110_1101;

4'd3 : codeout=7'b111_1001;

4'd4 : codeout=7'b011_0011;

4'd5 : codeout=7'b101_1011;

4'd6 : codeout=7'b101_1111;

4'd7 : codeout=7'b111_0000;

4'd8 : codeout=7'b111_1111;

4'd9 : codeout=7'b111_1011;

default: codeout=7'bx;

endcase

end

endmodule计数器

module w_2495_03_2(clkin, clr, Q, CO, upd, en, load, data); //十进制计数器

input clkin, clr, upd, en, load;

input [3:0] data;

output [3:0] Q;

reg [3:0]Q;

output wire CO;

always@(posedge clkin, posedge clr)

if(clr) //异步清零(为1时)

Q<=4'd0;

else if(!load) //同步置数,若为低电平则直接赋值

Q<=data;

else if(en) //en高电平,同步使能

begin

if(upd & load) //同步置数,加法计数,upd 1

begin

if(Q==4'd9)

Q<=4'd0;

else

Q<=4'd1+Q;

end

else if(load) //同步置数,减法计数 upd0

begin

if(Q==4'd0)

Q<=4'd9;

else

Q<=Q-4'd1;

end

end

assign CO = (upd&(Q==4'd9))|(~upd&(Q==4'd0)&~clr);

//(upd为高电平且Q为9)或者(upd为低电平且Q为0且clk为0)

endmodule

注意:因为我当时写的时候啥也不知道,但一般来说,时钟信号采用上升沿触发(posedge),而复位信号一般采用下降沿触发(negedge),所以开头可以改成:

always@(posedge clkin, negedge clr)

if(!clr) //异步清零

Q<=4'd0;四、仿真波形

1.加计数

文章来源地址https://www.toymoban.com/news/detail-448596.html

2.减计数

五、引脚分配表

二、引脚分配表(电路中的信号名称->主板器件名称->引脚号PIN)

| 信号名 |

主板器件 |

PIN |

信号名 |

主板器件 |

PIN |

|

| CO |

IO4 |

PIN_58 |

codeout[1] |

f |

PIN_110 |

|

| Q[3] |

IO3 |

PIN_54 |

codeout[0] |

g |

PIN_103 |

|

| Q[2] |

IO2 |

PIN_52 |

en |

SW1 |

PIN_31 |

|

| Q[1] |

IO1 |

PIN_50 |

load |

SW3 |

PIN_33 |

|

| Q[0] |

IO0 |

PIN_46 |

seg0 |

SEG0 |

PIN_119 |

|

| clkin |

CLK0 |

PIN_88 |

upd |

SW2 |

PIN_30 |

|

| clr |

SW0 |

PIN_24 |

data[3] |

SW7 |

PIN_44 |

|

| codeout[6] |

a |

PIN_112 |

data[2] |

SW6 |

PIN_39 |

|

| codeout[5] |

b |

PIN_100 |

data[1] |

SW5 |

PIN_42 |

|

| codeout[4] |

c |

PIN_104 |

data[0] |

SW4 |

PIN_32 |

|

| codeout[3] |

d |

PIN_111 |

||||

| codeout[2] |

e |

PIN_106文章来源:https://www.toymoban.com/news/detail-448596.html |

到了这里,关于1位十进制可逆计数、译码、显示电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!