数字电路基础(四) 数据分配器、数据选择器和数值比较器

一、数据分配器

在数据传输的过程中,数据选择器可以把某一路的数据分配到不同的数据通道上,这种电路称为数据分配器。简称DEMUX,一般有已鞥输入和多个输出。如下图所示是一个四路数据选择器的芯片集成图:

它可以将D送到数据变量选择的通道,下图是数据选择器的真值表:

可以看到,

A

A

A和

B

B

B两位数代表了输出路的二进制编码,被称为选择输入端。各路的函数表达式为:

W

0

=

D

A

B

‾

W_0=D\overline{AB}

W0=DAB

W

1

=

D

A

‾

B

W_1=D\overline{A}B

W1=DAB

W

2

=

D

A

B

‾

W_2=DA\overline{B}

W2=DAB

W

0

=

D

A

B

W_0=DAB

W0=DAB

二、数据选择器

数据选择器简称MUX。其逻辑功能是在地址选择信号的控制下,从多路数据中选择一路输出。

74153是一个双四选一数据选择器,下图是它的芯片引脚分布图:

其中 A 0 A_0 A0, A 1 A_1 A1是地址选择端, E ‾ \overline{E} E是使能端,只有当它输入为0时,数据选择器才可以工作,否则两个输出端将输出0。

74151是一个八选一数据选择器,下图是它的芯片引脚分布图:

E

E

E端为使能端,只有当它为0时,数据选择器才会工作,否则输出端输出0;由于是八位选择器,故需要

A

0

A_0

A0

A

1

A_1

A1

A

2

A_2

A2三位选择位(

2

3

=

8

2^3=8

23=8)下图是74151的功能表:

数据选择器的输出逻辑函数的形式是最小项之和的与或式,故可以用数据选择器实现任意逻辑函数。

三、数值比较器

数值比较器的作用是比较两个二进制数的大小的器件。

数值比较器如何实现比较?假设有两个四位二进制数

A

=

A

3

A

2

A

1

A

0

A=A_3A_2A_1A_0

A=A3A2A1A0和

B

=

B

3

B

2

B

1

B

0

B=B_3B_2B_1B_0

B=B3B2B1B0,比较这两个数的大小就要从最高位开始比较,如果最高位不相等,则可以说明最高位较大的那个数较大,最高位较小的那个数较小;如果最高位相等,则比较下一位,同样,如果这一位不相等,则说明这一位较大的那个数较大,这意味较小的那个数较小,如果这一位也相等,则继续比较下一位,直至分辨清楚这两个数的大小。

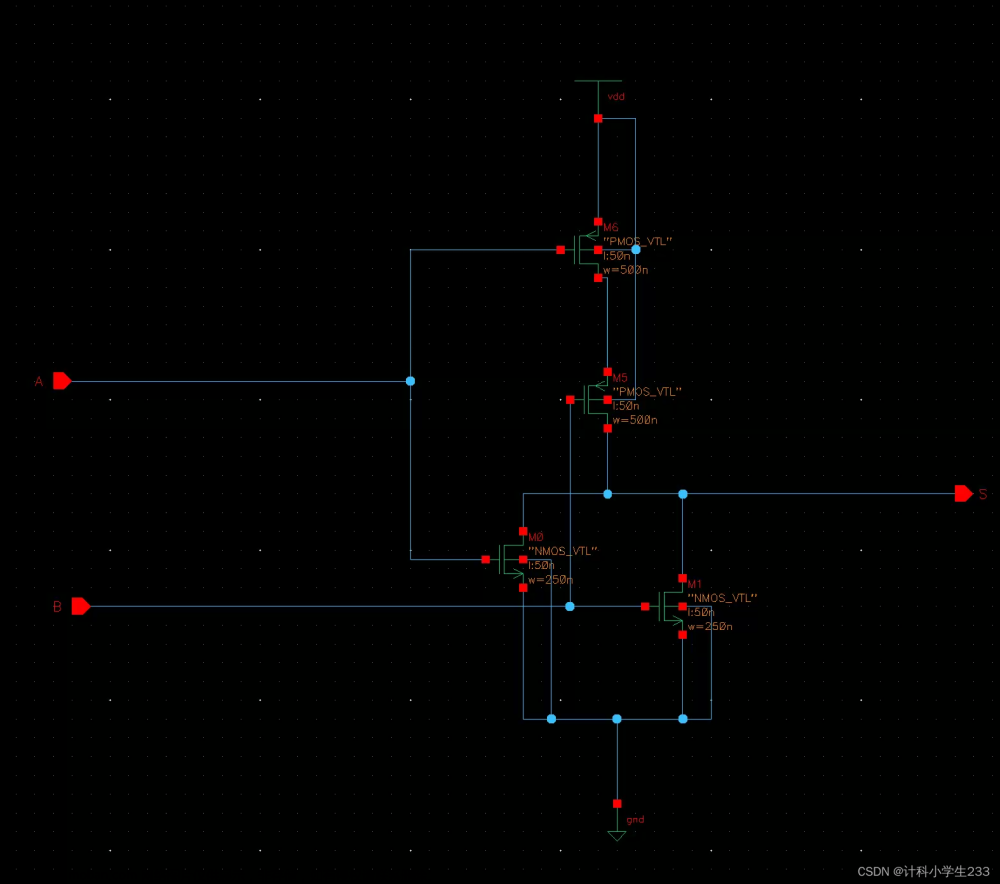

1.一位数值比较器

首先给出一位数值比较器的真值表:

可以根据真值表写出表达式:

(

A

i

=

B

i

)

=

A

i

⊕

B

i

‾

(A_i=B_i)=\overline{A_i\oplus B_i}

(Ai=Bi)=Ai⊕Bi

(

A

i

<

B

i

)

=

A

i

‾

B

i

(A_i<B_i)=\overline{A_i}B_i

(Ai<Bi)=AiBi

(

A

i

>

B

i

)

=

A

i

B

i

‾

(A_i>B_i)=A_i\overline{B_i}

(Ai>Bi)=AiBi

根据表达式连接逻辑图即可。

2.四位数值比较器

下图是四位数值比较器的真值表:

表中第2-3行说明只要最高位不相等,则可以判断大小

表中4-9行是当最高位相等时的情况,此时比较低位,最终也可以比较出大小

表中最后三行是两个数的各位都相等的情况,则此时的结果由级联输入端的状态决定,哪个级联输入端的输入为1,则对应的输出端的输出为1.文章来源:https://www.toymoban.com/news/detail-449061.html

初稿2022/5/7文章来源地址https://www.toymoban.com/news/detail-449061.html

到了这里,关于数字电路基础(四) 数据分配器、数据选择器和数值比较器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!