Vscode联合ModelSim检错

一、Vscode配置

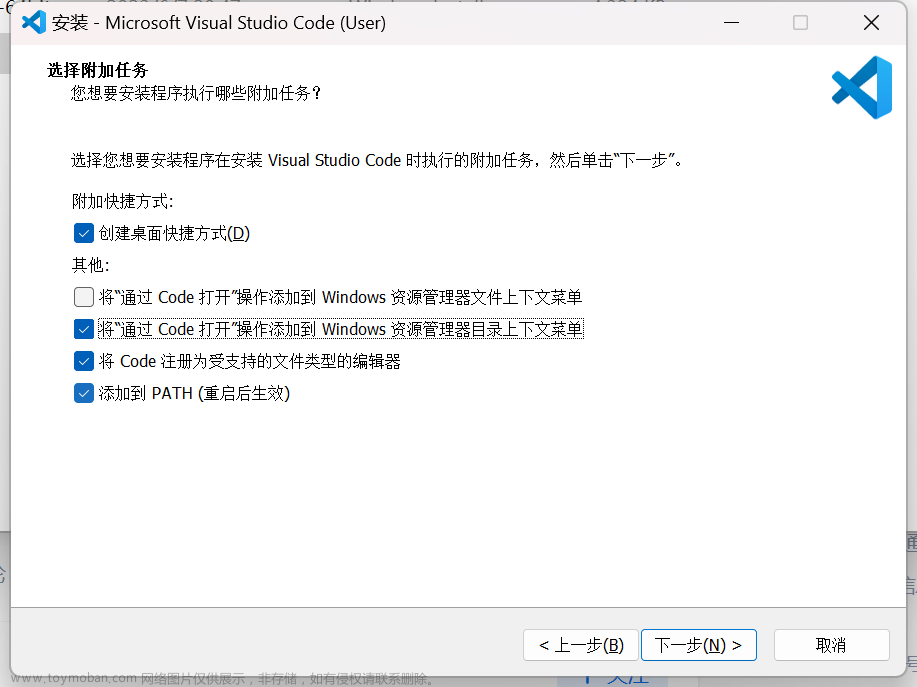

首先在 vs code 中安装支持 Verilog 的插件:

在 vs code 的 Extension 中搜索 Verilog,安装如下图所示的插件;

二、ModelSim语法检查器检查

Modelsim的安装破解本文不再赘述,可选的Modelsim有与Quartus II集成的ModelsimAltera 和单独的 Modelsim,安装 Quartus II 可以进行简单的仿真和 FPGA 的开发,集成一些FPGA 的 IP 等,根据自己的需求进行安装,任意一个软件都可以;

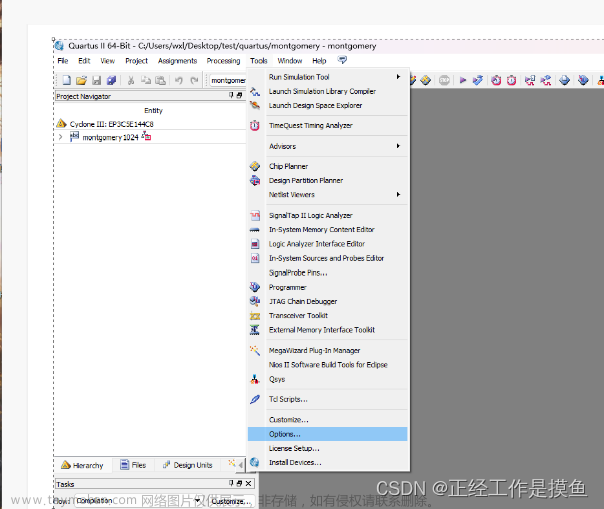

1.Modelsim-Altera 配置

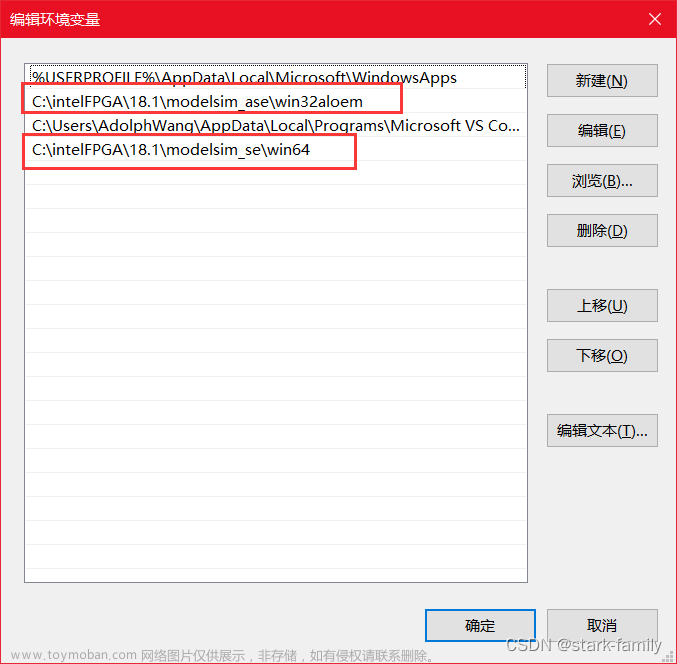

将 modelsim-Altera 安装目录下的 win32aloem 文件夹加入系统变量,因为要使用其中的 vlog.exe 的语法检查功能;

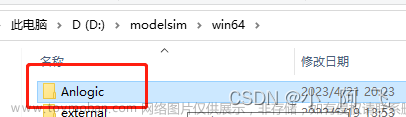

2.Modelsim 配置

将 modelsim 安装目录下的win64 文件夹加入系统变量,因为要使用其中的 vlog.exe 的语法检查功能;

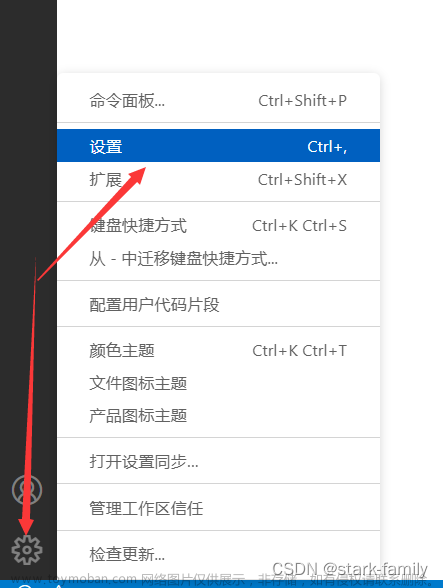

三、开始配置

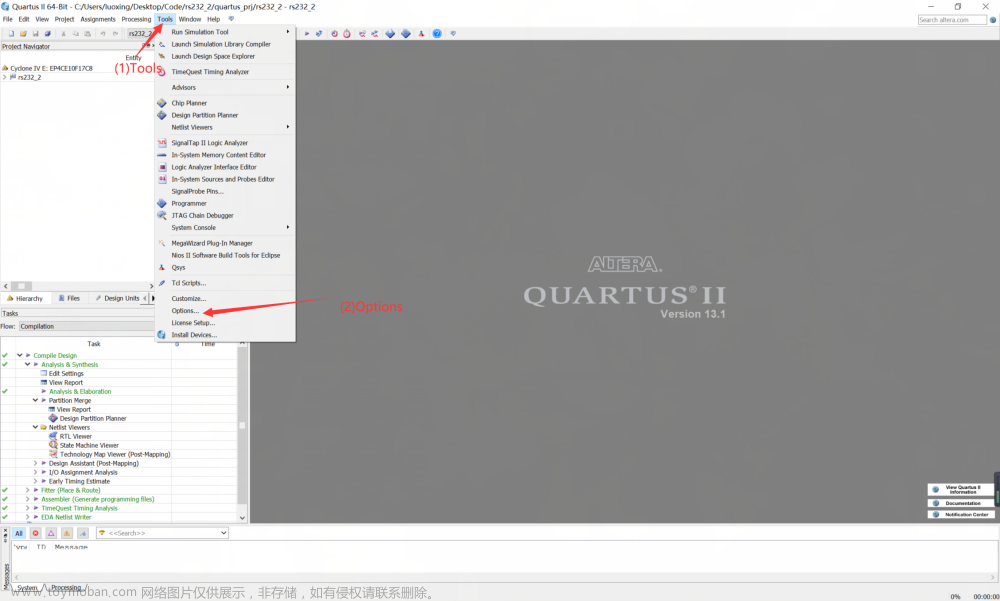

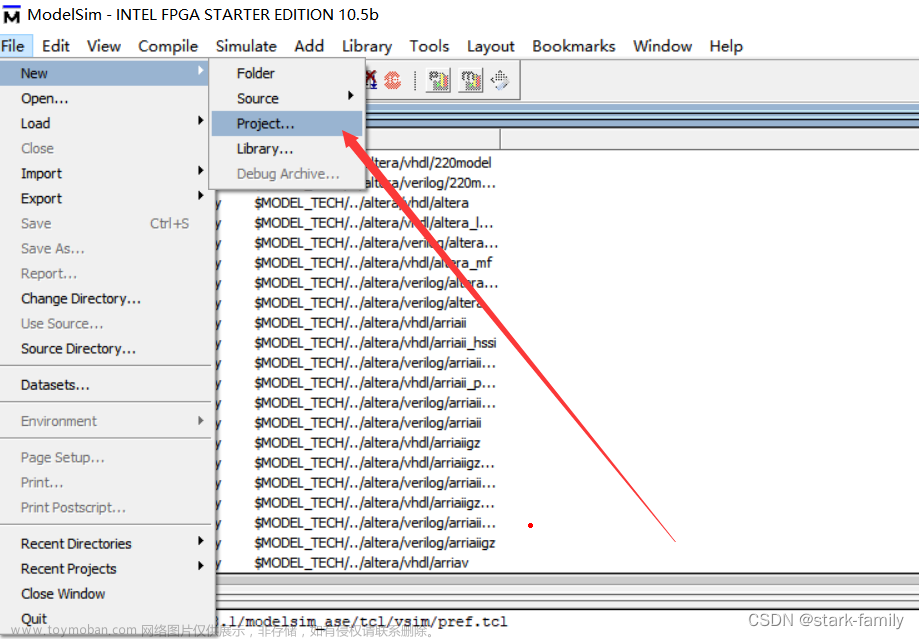

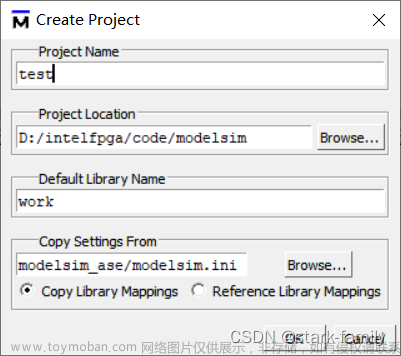

在完成以上之一的配置之后启动 modelsim-Altera 或者 modelsim 软件,因为都是一样的,所以下统称为 modelsim,启动 modelsim 后创建任意一个新的项目(项目路径不可包含中文与非法字符),如下图:

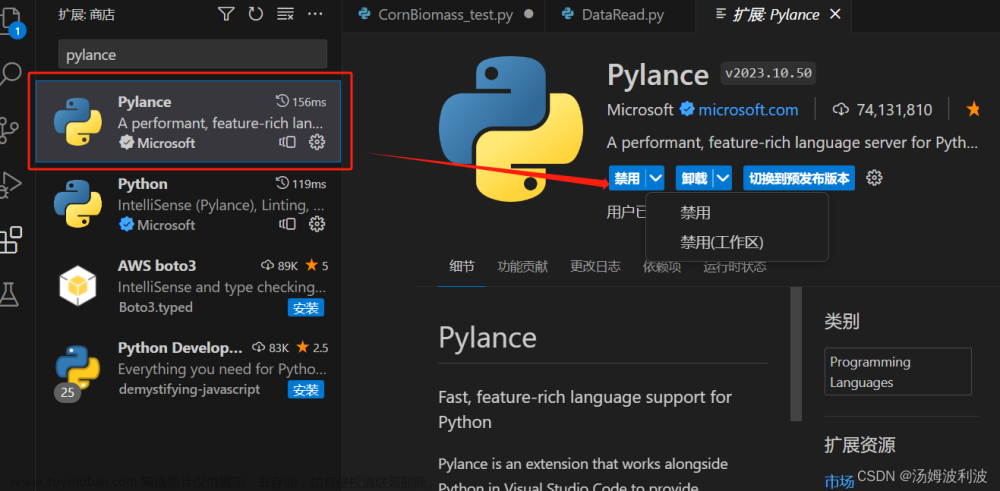

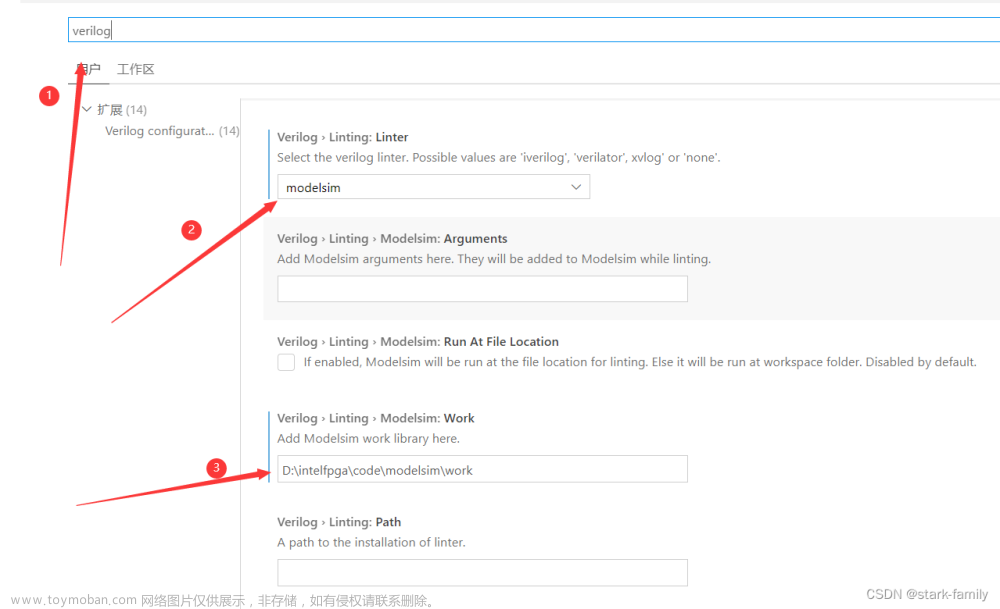

创建新项目后会在工程路经下下创建一个名为test 的文件夹,里面的work文件夹下面会有一个_info 文件(这个存放info的文件是不能删除的),将该目录复制到 vs code 设置中的 Verilog > Linting > Modelsim: Work 的设置之中,并将 Linter 的设置改为 modelsim,如下图:

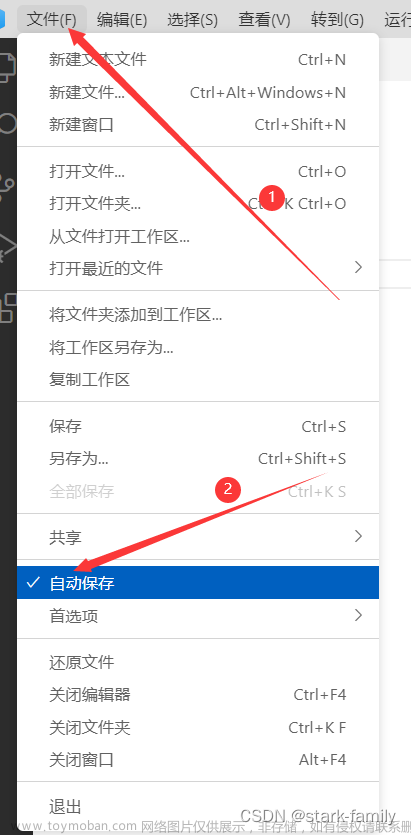

以上就完成了 modelsim 的语法检查和 vs code 的整合,我们接下将 vs code 设置成自动保存或者 Ctrl + S 可以实时地观察到文件的语法错误(但不会显示错误具体是什么)。

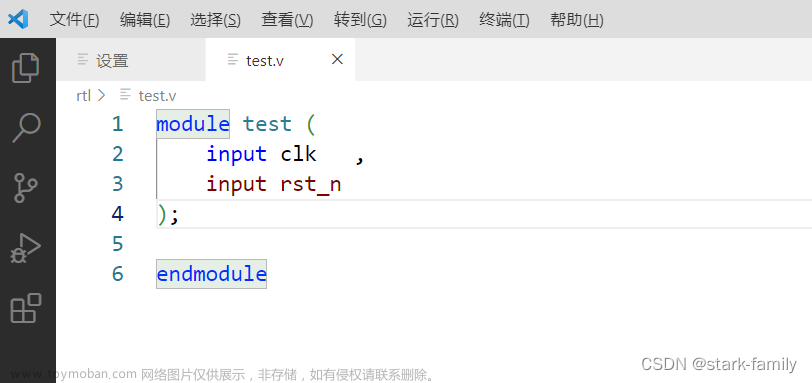

这里报错的原因是缺少一个逗号,出现了语法错误,会在附近的代码出现波浪线报错。(如遇设置好了但不能进行纠错,请关闭vscode重新打开一下)

语法正确是不会出现波浪线报错的。文章来源:https://www.toymoban.com/news/detail-449144.html

文章来源地址https://www.toymoban.com/news/detail-449144.html

文章来源地址https://www.toymoban.com/news/detail-449144.html

到了这里,关于VSCODE联合ModelSim语法检错的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!