一、多相滤波器,能够使用较低频率的时钟,实现较高数据率的数据滤波抽取。(咳咳 先正式一点)

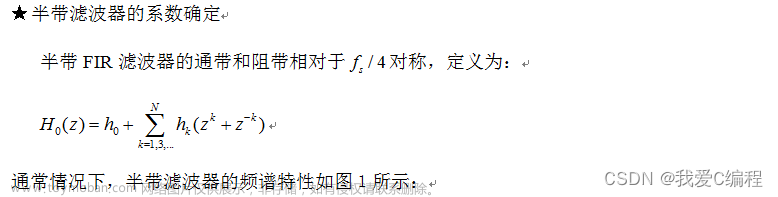

在实际的工程应用中, 为了降低硬件实现时的数据率, 往往需要进行多相分解。采用多相滤波结构,可利用Q个阶数较低的滤波来实现原本阶数较高的滤波,而且每个分支滤波器处理的数据速率仅为原数据速率的I/Q,这为工程上高速率实时信号处理提供了实现途径。多相分解是指将数字滤波器的传输函数H (z) 分解成若干不同相位的滤波器组。FIR滤波器h(n)的系统函数为

将冲激响应h (n) 的抽头系数分成Q组, 长度N是Q的整数倍;若N不是Q的整数倍, 需要对N进行补零, 使之满足整数倍的关系。那么H (z) 的多相分解结果为

其中Ek ()为每个分相的子滤波器。多相滤波器的一般结构为

采用多相结构实现滤波器的基本思想是将输入信号进行相应延迟后,分别送至Q个通道进行滤波,然后将每一支路滤波后的数据相加,得到最终输出结果。在使用多相滤波器完成滤波后进行D倍抽取,在实现时可以将延时和抽取结合在一起,采用此结构进行抽取滤波时将滤波器分成D相,在该结构中包括3个模块:(1)串并转换,将输入数据转换成D路并行信号;(2)多相滤波,将得到的D路信号进行滤波;(3)加法运算,将滤波后的信号相加得到最终输出信号。

二、以实际的双相滤波、二倍抽取为例

在AD变换前的过程就是升采样然后滤波并抽取的过程。

二相滤波器可以实现以aMHz的时钟来实现2aMHz数据率的处理,滤波完成输出后并实现二倍抽取。

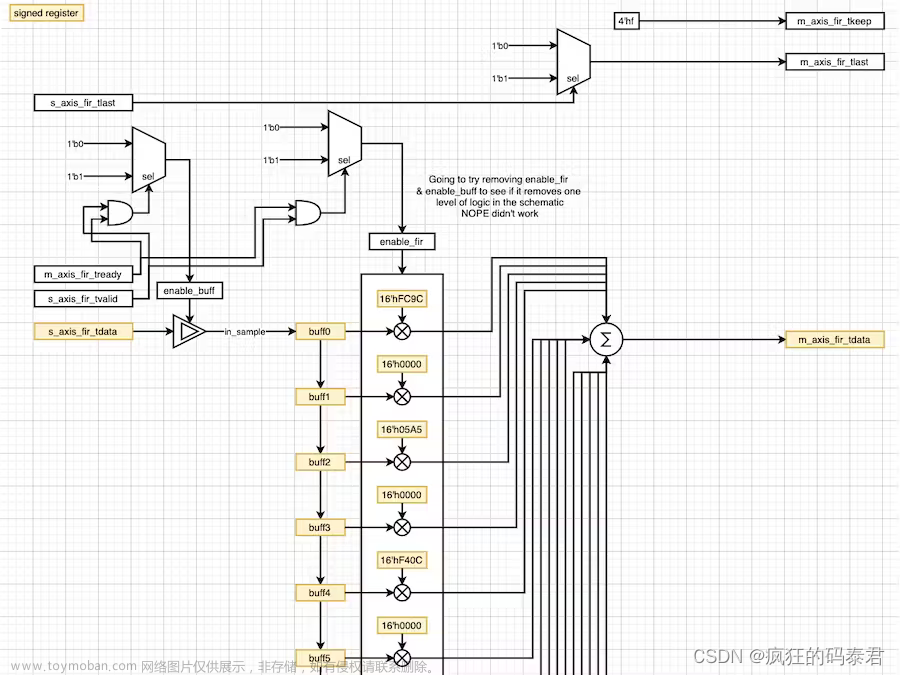

实现结构如下(有点简陋 各位见笑了)

在多相滤波器实现时将延时和抽取结合在一起,电子开关以频率FX每逆时针旋转一周,在每次转到p0(n)时,输出端就以频率FX/2送出一个y(m)样值。在开始时只有x(0)进入p0(n),p1(n)无信号,所以总输出y(0)= p0(n)x(0)=h(0)x(0)。逆时针旋转进入下一周期,电子开关转到p1(n),x(1)进入p1(n),p1(n)的输出为p1(0)x(1)=h(1)x(1),然后电子开关又转到p0(n),此时,x(2)进入p0(n)第一节,上一周期中进入p0(n)的x(0)移位到p0(n)的第二节,所以p0(n)的输出为p1(0)x(2)+ p1(1)x(0)= h(0)x(2)+ h(2)x(0),总的输出为y(1)= h(0)x(2)+ h(2)x(0)+ h(1)x(1)。依次可以推导出此结构实现了二倍抽取。

三、用Verilog实现一下下

首先MATLAB生成滤波器系数,然后腻那个旋转开关怎么实现呀!一个时钟信号aMHz,另一个时钟信号aMHz,哈哈哈,俩一样!

但是 CLK_1 = ~CLK_2

将2aMHz的数据直接接入两项滤波器里面,由于时钟上升沿有效,刚好第一个数据第一相读入,第二个数据第二项读入……

然后数据处理完后,两项都有输出,要实现同时相加,相加时钟选取时钟CLK_1,按上面所说的(下图),第二相数据输出早于第一相半个时钟周期,但是数据会保持一个时钟周期,在半个周期后等到第一相CLK_1的上升沿,相加输出。

always @ (posedge CLK_1) begin

if(!rst) begin

Data_out <= x'd0;

end

else begin

Data_out <= Data_1 +Data_2;

end哈哈哈哈,只会always begin end咋办!代码后面改改再贴。

文章来源:https://www.toymoban.com/news/detail-449949.html

文章来源地址https://www.toymoban.com/news/detail-449949.html

到了这里,关于Verilog实现多相滤波器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!