数字设计 FPGA 应用,第三章组合逻辑设计和 VIVADO 进阶,课程设计性质的作业题2

第二题:再建一个工程,调用该 IP 核实现 4 输入逻辑函数f=∑wxyz(1,3,6,7,11,13,14)。对该工程进行仿真测试(必须)

使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

第一题及生成的IP核见链接:

第一题:实现8选1的数据选择器74HC151

问题分析

74HC151及其功能表如下图所示:

- 当EN_L=0时,74HC151的输出逻辑表达式可以写为:

Y=(C’B’A’) · D0+(C’B’A)· D1+(C’BA’)· D2+(C’BA)· D3+(CB’A’)· D4+(CB’A)· D5+(CBA’)· D6+(CBA)· D7 - 将给定的逻辑函数 f=∑wxyz(1,3,6,7,11,13,14)写为:

f=w’x’y’z+w’x’yz+w’xyz’+w’xyz+wx’yz+wxy’z+wxyz’

3.逻辑函数式对应1中的逻辑表达式写成如下格式:

f=(w’x’y’)· z+(w’x’y)· z+(w’xy’)· 0+(w’xy)· (z+z’)+(wx’y’)· 0+(wx’y)· z+(wxy’)· z+(wxy1)· z’

Y与f式相对应即可得出74HC151的输入:

令 C=w、B=x、A=y、D0=z、D1=z、D2=0、D3=1、D4=0、D5=z、D6=z、D7=z’

如下图所示: 文章来源:https://www.toymoban.com/news/detail-450059.html

文章来源:https://www.toymoban.com/news/detail-450059.html

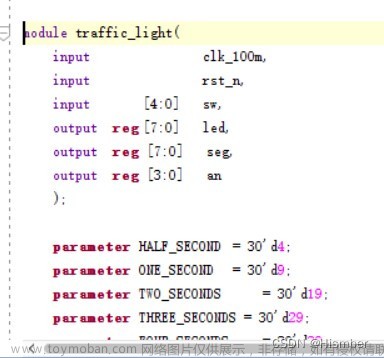

代码实现

- Verilog代码

`timescale 1ns / 1ps

//

// Create Date: 2022/09/16 12:42:49

// Design Name:

// Module Name: f_74hc151_ip

// Revision 0.01 - File Created

// Additional Comments:

//

//

//文章有用的话记得给靓仔点个赞表示鼓励哟~

module f_74hc151_ip(w,x,y,z,f);

input w,x,y,z;

output f;

wire Y;

wire Y_;

wire[7:0] D;

// D = {D7,D6,D5,D4,D3,D2,D1,D0};

assign D[0]=z,D[1]=z,D[2]=0,D[3]=1,D[4]=0,D[5]=z,D[6]=z,D[7]=~z;

//运行出错:assign D = {~z,z,z,0,1,0,z,z};

assign f=Y;

v_74hc151_0 uut(

.E_(0),

.S({w,x,y}),

.D(D),

.Y(Y),

.Y_(Y_)

);

endmodule

- 仿真文件

`timescale 1ns / 1ps

//

// Create Date: 2022/09/16 12:58:16

// Design Name:

// Module Name: sim_74hc151_ip

// Revision 0.01 - File Created

// Additional Comments:

//

//

//文章有用的话记得给靓仔点个赞表示鼓励哟~

module sim_74hc151_ip(

);

reg a,b,c,d;

wire f;

f_74hc151_ip tt(a,b,c,d,f);

initial begin

a=0;b=0;c=0;d=0;

end

always #10 {a,b,c,d} = {a,b,c,d}+1;

endmodule

仿真结果:

3. 约束文件文章来源地址https://www.toymoban.com/news/detail-450059.html

## Switch

set_property PACKAGE_PIN P5 [get_ports w]

set_property IOSTANDARD LVCMOS33 [get_ports w]

set_property PACKAGE_PIN P4 [get_ports x]

set_property IOSTANDARD LVCMOS33 [get_ports x]

set_property PACKAGE_PIN P3 [get_ports y]

set_property IOSTANDARD LVCMOS33 [get_ports y]

set_property PACKAGE_PIN P2 [get_ports z]

set_property IOSTANDARD LVCMOS33 [get_ports z]

## LED

set_property PACKAGE_PIN F6 [get_ports f]

set_property IOSTANDARD LVCMOS33 [get_ports f]

- 运行结果

下图展示了wxyz=0110(=6)时的结果,LED灯 F6点亮,一般仿真正确则运行也会正确,其他情况显示与仿真结果一致。

到了这里,关于EGO1—使用8选1数据选择器实现四输入逻辑函数 f=∑wxyz(1,3,6,7,11,13,14)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!