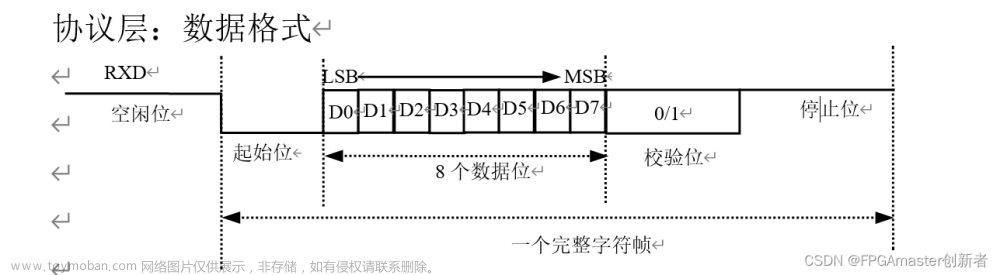

handshake握手电路

- 跨时钟域处理是个很庞大并且在设计中很常出现的问题

- 握手(handshake)是用来处理信号跨时钟域传递的一个有效的方法

- 使用握手协议方式处理跨时钟域数据传输,只需要对双方的握手信号(req和ack)分别使用脉冲检测方法进行同步

- req与ack就和TCP传输之前的三次握手协议类似,是一种有来有往的信息请求与应答

- 具体实现中

- 假设req、ack、data总线在初始化时都处于无效状态,发送域先把数据放入总线,随后发送有效的req信号给接收域

- 接收域在检测到有效的req信号后锁存数据总线,然后回送一个有效的ack信号表示读取完成应答

- 发送域在检测到有效ack信号后撤销当前的req信号,接收域在检测到req撤销(需要进行边沿检测)后也相应撤销ack信号,此时完成一次正常握手通信

- 此后,发送域可以继续开始下一次握手通信,如此循环

- 该方式能够使接收到的数据稳定可靠,有效的避免了亚稳态的出现,但控制信号握手检测会消耗通信双方较多的时间

使用握手信号实现跨时钟域数据传输

- 题目来源于牛客网刷题库

- https://www.nowcoder.com/practice/2bf1b28a4e634d1ba447d3495134baac

接口信号图

文章来源:https://www.toymoban.com/news/detail-450617.html

文章来源:https://www.toymoban.com/news/detail-450617.html

题目描述

- 分别编写一个数据发送模块和一个数据接收模块,模块的时钟信号分别为clk_a,clk_b

- 两个时钟的频率不相同。数据发送模块循环发送0-7,在每个数据传输完成之后,间隔5个时钟,发送下一个数据,在两个模块之间添加必要的握手信号,保证数据传输不丢失

- data_req和data_ack的作用说明:

- data_req表示数据请求接受信号,当data_out发出时,该信号拉高,在确认数据被成功接收之前,保持为高,期间data应该保持不变,等待接收端接收数据

- 当数据接收端检测到data_req为高,表示该时刻的信号data有效,保存数据,并拉高data_ack

- 当数据发送端检测到data_ack,表示上一个发送的数据已经被接收,撤销data_req,然后可以改变数据data,等到下次发送时,再一次拉高data_req

解题思路

- 分别编写数据发送模块与数据接收模块

- 对于数据发送模块

- 数据发送模块会向数据接收模块发送req请求,表示数据已经准备好,可以发送给接收模块

- 收到接收模块的ack应答信号,表示数据接收模块同时已经接收到数据,此时需要撤销req请求,改变发送数据data,准备下一次的发送

- 对于数据接收模块

- 数据接收模块收到数据发送模块的req信号之后,皆可以进行数据data的接收

- 当数据接收模块将data接收保存之后,就需要向数据发送模块返回ack信号,表示当前数据data已成功接收,无需继续保持,可以准备下一个要传输的数据了

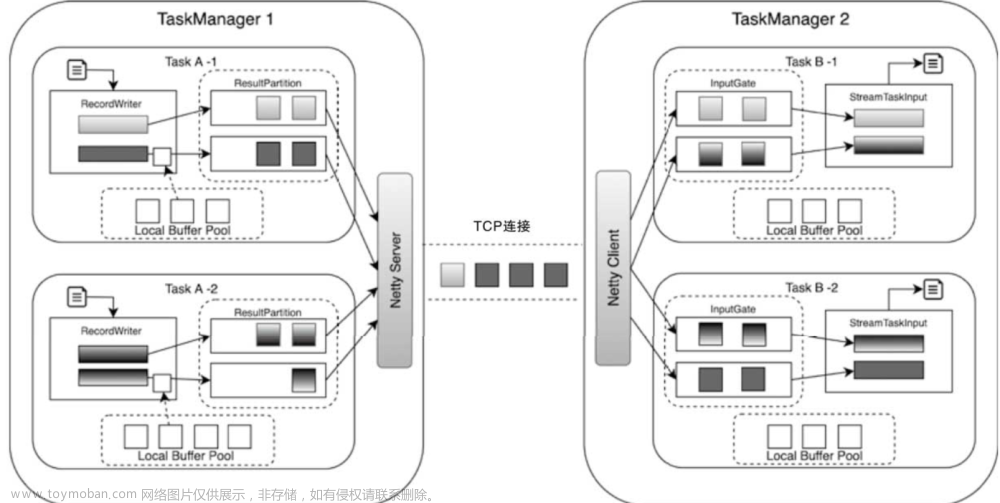

- 对于两模块的跨时钟问题

- 由于两模块具有不同的时钟域,故在进行数据传递时,若直接使用接收到的信号,会产生亚稳态问题,故在两个模块中都需要对不同时钟域传递而来的信号进行同步

代码设计

数据发送模块data_driver

`timescale 1ns/1ns

// 数据发送模块

module data_driver(

input clk_a,

input rst_n,

input data_ack,

output reg [3:0] data,

output reg data_req

);

reg data_ack_1;

reg data_ack_2;

reg [2:0] count;

// 打两拍消除亚稳态

always @(posedge clk_a or negedge rst_n) begin

if (~rst_n) begin

data_ack_1 <= 1'b0;

data_ack_2 <= 1'b0;

end else begin

data_ack_1 <= data_ack;

data_ack_2 <= data_ack_1;

end

end

// 输出数据data

always @(posedge clk_a or negedge rst_n) begin

if (~rst_n) begin

data <= 4'b0;

end else if (data_ack_1 && !data_ack_2) begin

if (data == 4'd7) begin

data <= 4'd0;

end else begin

data <= data + 1;

end

end else begin

data <= data;

end

end

// count计数模块

always @(posedge clk_a or negedge rst_n) begin

if (~rst_n) begin

count <= 3'b0;

end else if (data_ack_1 && !data_ack_2) begin

count <= 3'b0;

end else if (data_req) begin

count <= count;

end else begin

count <= count + 1;

end

end

// data_req信号

always @(posedge clk_a or negedge rst_n) begin

if (~rst_n) begin

data_req <= 1'b0;

end else if (count == 3'b100) begin

data_req <= 1'b1;

end else if (data_ack_1 && !data_ack_2) begin

data_req <= 1'b0;

end else begin

data_req <= data_req;

end

end

endmodule

数据接收模块data_receiver

`timescale 1ns/1ns

// 数据接收模块

module data_receiver(

input clk_b,

input rst_n,

input [3:0] data,

input data_req,

output reg data_ack

);

reg data_req_1;

reg data_req_2;

reg [3:0] data_in;

// 打两拍消除亚稳态

always @(posedge clk_b or negedge rst_n) begin

if (~rst_n) begin

data_req_1 <= 1'b0;

data_req_2 <= 1'b0;

end else begin

data_req_1 <= data_req;

data_req_2 <= data_req_1;

end

end

// data_ack信号

always @(posedge clk_b or negedge rst_n) begin

if (~rst_n) begin

data_ack <= 1'b0;

end else if (data_req_1) begin

data_ack <= 1'b1;

end else begin

data_ack <= 1'b0;

end

end

// 接收data数据到data_in

always @(posedge clk_b or negedge rst_n) begin

if (~rst_n) begin

data_in <= 4'b0;

end else if (data_req_1 && !data_req_2) begin

data_in <= data;

end else begin

data_in <= data_in;

end

end

endmodule

testbench

`timescale 1ns / 1ps

`include "data_driver.v"

`include "data_receiver.v"

module tb_handshake;

// data_driver Parameters

parameter PERIOD1 = 10;

parameter PERIOD2 = 20;

// data_driver Inputs

reg clk_a = 0 ;

reg rst_n = 0 ;

// data_receiver Inputs

reg clk_b = 0 ;

wire [3:0] data;

initial

begin

forever #(PERIOD1/2) clk_a=~clk_a;

end

initial

begin

forever #(PERIOD2/2) clk_b = ~clk_b;

end

initial

begin

#(PERIOD1*2) rst_n = 1;

end

data_driver u_data_driver (

.clk_a ( clk_a ),

.rst_n ( rst_n ),

.data_ack ( data_ack ),

.data ( data [3:0] ),

.data_req ( data_req )

);

data_receiver u_data_receiver (

.clk_b ( clk_b ),

.rst_n ( rst_n ),

.data ( data [3:0] ),

.data_req ( data_req ),

.data_ack ( data_ack )

);

initial

begin

$dumpfile("handshake.vcd");

$dumpvars;

#1000

$finish;

end

endmodule

波形

文章来源地址https://www.toymoban.com/news/detail-450617.html

文章来源地址https://www.toymoban.com/news/detail-450617.html

- 波形解释

- 按照题目要求,data循环发送0~7

- 按照题目要求,在一个data成功发送后,需要间隔5个时钟周期,在data_req信号由高到低再到高,中间间隔为5个clk_a周期,即为5个数据发送模块的时钟间隔

- 从整个系统的宏观角度进行观测

- 在clk_a时钟下的data_req拉高发送请求后,clk_b时钟下的data_ack拉高表示数据已接收,紧接着data_req拉低进行数据准备阶段的间隔

- 在clk_b时种下的data_ack拉高发送反馈后,clk_a时钟下的data_req拉低表示当前数据已停止发送,紧接着data_ack持续拉高表示可以发送新数据

- 从数据发送端进行观测

- 发送数据的同时,data_req持续拉高,表示正在持续进行当前数据的发送,当接收到data_ack信号后,data_req拉低并停止当前数据的发送,准备新数据

- 固定间隔之后,再次进行数据的请求发送与数据发送

- 从数据接收端进行观测

- 收到data_req信号,开始接收发送来的data数据,当数据成功接收保存后,返回data_ack表示可以接收新数据

- 反馈data_ack信号的一段时间后,会重新接收到data_req信号表示新数据已经发送,开始新一轮的数据接收工作

到了这里,关于【Verilog】握手信号实现跨时钟域数据传输-handshake的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!