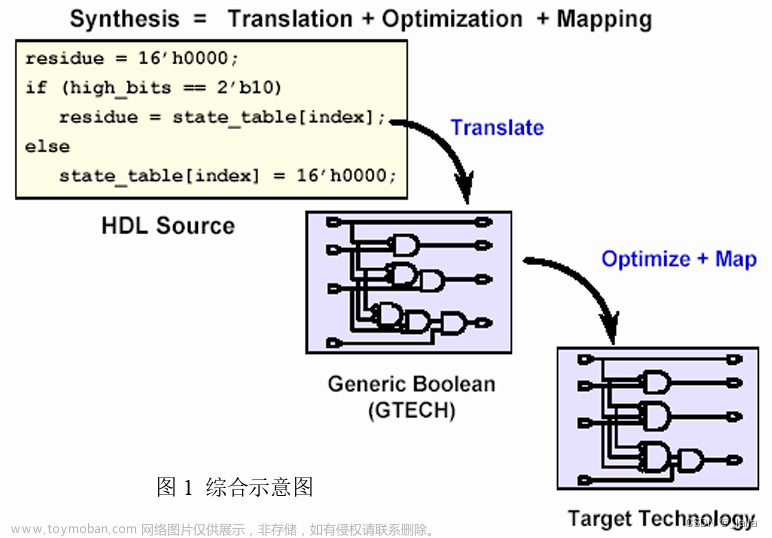

一名优秀的IC设计工程师需要懂综合,清楚自己设计的代码与底层的电路的对应关系,明白综合工具对代码的优化方案从而设计出更优PPA(performance,power,area)的电路。同时综合在代码和实际门级电路之间扮演着重要的角色,DC是用于将RTL代码转换成可用于布局布线的网表文件,而可用于布局布线的网表文件需要满足时序要求、面积要求、功耗要求。DC综合可以先从必要的步骤开始,再针对具体的error和warning、violation进行分析解决,若需要增加约束、设置再增加,但前提是需要将所有的error和warning、violation都报出来。

下面记录一种参考模板,在相应的路径下新建一个SYN的文件夹用于存放不同工程的与综合相关的文件。

目录

1 DC综合的总体介绍

2 read_rtl.tcl

3 setup_lib.tcl

4 sta_rules.tcl

5 opt_rules.tcl

6 setup_dc.tcl

7 run_dc.tcl

1 DC综合的总体介绍

>mkdir SYN

>cd SYN

SYN>ls

project1 project2 project3

SYN>cd project1

/SYN/project1>ls

logs outputs reports scripts project1_flist

/SYN/project1>cd scripts

/SYN/project1>ls

opt_rules.tcl read_rtl.tcl run_dc.tcl setup_dc.tcl setup_lib.tcl sta_rules.tcl

按照综合步骤对以上文件进行说明或者举例说明。综合的基础步骤如下所示:

1 读入需要综合的rtl文件,即编写的rtl代码的.v文件——read_rtl.tcl,并生成相应的log文件

2 读入与底层电路对应的.db库文件——setup_lib.tcl,并生成相应的log文件(S家的脚本中可能没有这一个显示的步骤,因为它可以通过执行时自动加载.synopsys_setup.setup的隐形文件(文件名可能记不清楚了,待后续想起来再修改),这种方式有它的好处,但推崇显示的表示,即可让后来人一看就清楚,且修改库文件找起来也方便)

3 将读入的.v文件和.db文件link起来,并生成相应的log文件

4 读入设置综合模式或模型的文件——setup_dc.tcl

5 读入设置约束(包括时钟约束、输入输出约束等约束)的文件——sta_rules.tcl,并生成相应的log文件

6 读入设置优化的文件——opt_rules.tcl

7 进行compile之前的check,包括timing和design的check,生成相应的log文件

8 进行compile

9 进行compile之后的check,包括timing和design的check,生成相应的log文件

10 修改命名规则和使修改后的命名规则生效

11 生成相应的文件和报告

以上11个基础步骤对应下图中画红色下划线的语句

12 执行脚本文件——run_dc.tcl

注:project1_flist文件夹中是一个要综合的RTL.v的flist清单,下面会说明。

在以上7种文件都准备好后,在terminal中之行如下的操作命令

/SYN>dc_shell-t

dc_shell>source scripts/run_dc.tcl

或者以上两条指令合成一条指令,如下:

/SYN>dc_shell-t -f scripts/run_dc.tcl

待运行结束后,可以输入report_timing,report_area等命令用以查看综合后的时序报告、面积报告。退出综合命令界面使用exit命令。

此时可以在logs,outputs,reports文件夹中查看综合执行记录、综合输出结果和综合报告。其中reports中有综合后的面积报告、时序报告;outputs中有.vg(后缀也可以改写为.v,可根据自己的习惯使用)的门级网表文件、.sdc的静态时序约束报告,标准延时约束文件、包含基本的布局物理信息的.ddc文件,为方便退出后再次恢复之前DC执行的命令、状态等的文件、标记DC优化处理信息并用于形式验证的.svf文件、从前端到后端的.saifmap的映射文件(需要确认一下)。

综合的网表文件中需要确:认每条路径都被约束了,即不存在unconstrained的路径;不存在setup violation;不存在设计意图之外的combinational loop;不存在设计意图之外的latch;无assign语句;网表中无“SEQGEN”的通用表示。

2 read_rtl.tcl

source /project/xiaoming/view2/vision.flist

analyze -format verilog $top_flist

elaborate $top_design

上面的vision.flist如下所示:

set top_flist{ \

/project/xiaoming/view2/RTL/module1.v \

/project/xiaoming/view2/RTL/module2.v \

-f /project/xiaoming/common/common.f \

/project/xiaoming/view2/RTL/module3.v \

}

3 setup_lib.tcl

set search_path "$search_path WORK \

. \

/xiaoming/view2/RTL_file_directory \

/xiaoming/view2/lib_file_directory \

/xiaoming/view2/db_file_directory \

"

set synthetic_library dw_foundation.sldb

set target_library "1st.db \

2nd.db \

3rd.db \

4th.db \

"

set link_library "* $target_library"

set link_library "* $link_library rom1.db"

set link_library "* $link_library rom2.db"

set link_library "* $link_library ram1.db"

set link_library "* $link_library ram2.db"

set symbol_library generic.sdb

define_design_lib WORK -path ./WORK

注:关于black box的库文件,如ram、rom的库文件不放在target library中,而是放在link library中。

4 sta_rules.tcl

####设置需要的时钟周期

set clk1_period 3.78

set clk2_period 10

#####Creat clock port (默认时钟的占空比为50%,如存在其他占空比需要进行设置。这里使用的是命令是create_clock,可以查找该命令的使用规则)

creat_clock clock_a -period $clk2_period [get_port i_input_a]

creat_clock clock_b -period $clk2_period [get_port i_input_b]

creat_clock clock_c -period $clk1_period [get_port i_input_c]

#########creat virtual clock (如果需要的话,虚拟时钟不需要Port)

creat_clock -name virtual_clock -period $clk4_period

##########generated clock (模块内部存在时钟生成模块,即用端口输入时钟生成其他需要的时钟的模块。这里使用的是create_generated_clock命令)

create_generated_clock -divide_by 2 -name "gen_clk1" -source clock_c [get_pins u_module_a/o_clk1] -master clock_c

###function mode (比如scan和dft)

set_case_analysis 0 scan_reg_sel

set_case_analysis 0 scan_reg_rst_b

set_case_analysis 0 dft_mode

#####################

###clock group 设置clocks之间的关系,同步/异步,logically/physically (这里用到的命令是set_clock_groups)

###########################

set_clock_groups -logically exclusive

-group [get_clocks {clock_b}] \

-group [get_clocks {clock_c}] \

-group [get_clocks {clock_d1 clock_d2 clock_d3}] \

-group [get_clocks {clock_e1 clock_e2 clock_e3 clock_e4 clock_e5}]

##set clock uncertainty

###############################

set CLK2_UNC [expr $clk2_period*0.2]

set CLK1_UNC [expr $clk1_period*0.2]

set_clock_uncertainty $CLK2_UNC -setup [get_clocks clock_a]

set_clock_uncertainty $CLK1_UNC -setup [get_clock clock_b]

#################################

##Inputs / Outputs

#####################################

set input1_delay_min [expr $clk3_period*0.3]

set input1_delay_max [expr $clk3_period*0.4]

set output1_delay_min [expr $clk2_period*0.3]

set output1_delay_max [expr $clk2_period*0.4]

set s0_in_portlist {

s0_in_1 \

s0_in_2 \

s0_in_3 \

}

set s0_out_portlist {

s0_out_1 \

s0_out_2 \

s0_out_3 \

}

set_input_delay -add_delay $input1_delay_min -clock clock_f -min [get_ports $s0_in_portlist]

set_input_delay -add_delay $input1_delay_max -clock clock_f -max [get_ports $s0_in_portlist]

set_output_delay -add_delay $output1_delay_min -clock clock_a -min [get_port $s0_out_portlist]

set_output_delay -add_delay $output1_delay_max -clock clock_a -max [get_port $s0_out_portlist]

5 opt_rules.tcl

set dont_use_list "\

*/*TIE* \

*/DEL* \

*/*DF*CSN* \

"

foreach cell $dont_use_list {

set_dont_use [get_lib_cells $cell]

}

set_driving_cell -lib_cell BUFFD16BWP7T30P140 -pin Z -no_design_rule [all_inputs]

#output load

set port_load [expr 5*[load_of tcbn22ullbwp7t30p14ssg0p72v125c_ccs/BUFFD16BWP7T30P140/I]]

set_load $port_load [all_outputs]

###################

#clock gate

##################

set_clock_gating_check -setup 0.45 -hold 0.3

####################

#wire load

##################

set auto_wire_load_selection false

remove_attribute [get_libs] default_wire_load

remove_wire_load_model [get_designs]

set_wire_load_model -name ZeroWireload

set_wire_load_mode top

###########################

#Operating environment

##############################

set_operating_conditions ssg0p72v125c

###################################

#DRC rule

###############################

set_max_fanout 35 [all_designs]

set_clock_transition 0.2 [all_clocks]

set_max_transition 0.2 [current_design]

#############################

#area optimization

#############################

set_max_area 0

#########################################

#dont touch

################################

#set_dont_touch u_pmu_cgu/x_STD_OCC_ae_buf/x_STD_OCC_clkbuf

#set_ideal_network [all_clocks]

set_dont_touch_network [all_clocks]

#set_dont_touch [get_cells u_alg_te_top/u_tpu_chnbfu/ASIC_*]

6 setup_dc.tcl

set_app_var case_analysis_with_logic_constants true

set_app_var compile_seqmap_propagate_high_effort true

set_app_var compile_auto_ungroup_count_leaf_cells false

set_app_var compile_enable_register_merging false

set_app_var compile_state_reachability_high_effort_merge false

set_app_var hdlin_infer_multibit default_all

set enable_recovery_removal_arcs true

7 run_dc.tcl

set hostname [sh hostname]

set starttime [clock seconds]

#####ENV propagation###########

set top_design [getenv "DESIGN_TOP"]

#################################

###Pre setup

#################################

if {![file exists ../$SYN_WA/logs]} {exec mkdir ../$SYN_WA/logs;}

if{![file exists ../$SYN_WA/reports]} {exec mkdir ../$SYN_WA/reports;}

if {![file exists ../$SYN_WA/outputs]} {exec mkdir ../$SYN_WA/outputs;}

set_svf ../$SYN_WA/outputs/${top_design}.svf

source -e -v ../../SYN/scripts/setup_dc.tcl

source -e -v ../../SYN/scripts/setup_lib.tcl > ../$SYN_WA/logs/setup_lib.log

######################################

###Read and Elaborate Design

#######################################

source -e -v ../../SYN/scripts/read_rtl.tcl > ../$SYN_WA/logs/read_rtl_list.log

set_compile_directives [get_designs {syn_reset_reg}] -constant_propagation false

current_design ${$top_design}

set verilogout_no_tri true

set_register_merging [current_design] false

set_critical_range 0.72 [current_design]

set_leakage_optimization false

link > ../$SYN_WA/logs/link_check.log

set uniquify_naming_style "${top_design}_%s_%d"

uniquify -force

check_design > ../$SYN_WA/reports/check_design.rpt

set_attribute [get_libs "tcbn22ullbwp7t35p140hvt*"] default_threshold_voltage_group 7t35p140hvt -type string

set_attribute [get_libs "tcbn22ullbwp7t30p140mblvt*"] default_threshold_voltage_group 7t30p140mblvt -type string

###############################################

####Optimization Constraints

################################################

source -e -v ../../SYN/scripts/sta_ruls.tcl >../$SYN_WA/logs/vision_sdc.log

source -e -v ../../SYN/scripts/opt_rules.tcl >../$SYN_WA/logs/opt_rules.log

write_sdc -nosplit -version 2.0 ../$SYN_WA/outputs/${top_design}.sdc

check_timing > ../$SYN_WA/reports/check_timing_beforecompile.rpt

############################################

##Compile Design and Optimization Design

###########################################

set_app_var verilogout_equation false

set_fixmultiple_port_nets -all -feedthroughs -buffer_constant [get_desgins *]

set_flatten -design *post_disc_code_error*

set_flatten -design *post_calc_dft*

set_flatten -design *post_disc_phase_error*

set_flatten -design *post_crossdot*

compile_ultra -scan -no_autoungroup -no_seq_output_inversion -gate_clock

check_design > ../$SYN_WA/reports/check_design_aftercompile.rpt

define_name_rules verilog -last_restricted _ -remove_chars

change_names -rule verilog -hier

write -f ddc -hier -output ../$SYN_WA/outputs/${top_design}_pre.ddc

write -f verilog -hier -output ../$SYN_WA/outputs/${top_design}.vg

write_sdc -nosplit -version 2.0 ../$SYN_WA/outputs/${top_design}.sdc

report_area -hierarchy -nosplit >../$SYN_WA/reports/debug_area.summary.rpt

report_area -hierarchy > ../$SYN_WA/reports/debug_area.rpt

report_timing -nworst 1000 -net -cap -transition > ../$SYN_WA/reports/report_timing.rpt

check_timing > ../$SYN_WA/reports/check_timing.rpt

report_constraint -all_violatiors -nosplit > ../$SYN_WA/reports/debug_timing.summary.rpt

report_constraint -all_violators -verbose >../$SYN_WA/reports/debug_timing.rpt

report_area > ../$SYN_WA/reports/${top_design}-compile.area

report_cell > ../$SYN_WA/reports/${top_design}-compile.cell

report_clock > ../$SYN_WA/reports/${top_design}-compile.clocks

report_power > ../$SYN_WA/reports/${top_design}-compile.power

report_power -hier -level 1 > ../$SYN_WA/reports/${top_design}-compile_level1.power

report_power -hierarchy -level 1 > ../$SYN_WA/reports/${top_design}-compile_hier.power

report_qor > ../$SYN_WA/reports/${top_design}-compile.qor

report_resources > ../$SYN_WA/reports/${top_design}-compile_resources

report_clock_gating > ../$SYN_WA/reports/${top_design}-compile_clockgate

report_clock_gating_check > ../$SYN_WA/reports/${top_design}-compile_clockgate_check

report_clock_gating -ungated > ../$SYN_WA/logs/clock_gating_ungated.log

report_clock_gating -hier > ../$SYN_WA/logs/clock_gating_check.log

report_threshold_voltage_group > ../$SYN_WA/reports/threshold_voltage_group.rpt

source ../../update_tag.tcl

update_tag SYN_TAG

date

exit文章来源:https://www.toymoban.com/news/detail-450671.html

个人学习记录,如有侵权请联系删除,如有错误欢迎指出、拍砖。文章来源地址https://www.toymoban.com/news/detail-450671.html

到了这里,关于IC设计中的DC综合学习记录——模板记录的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!