目录

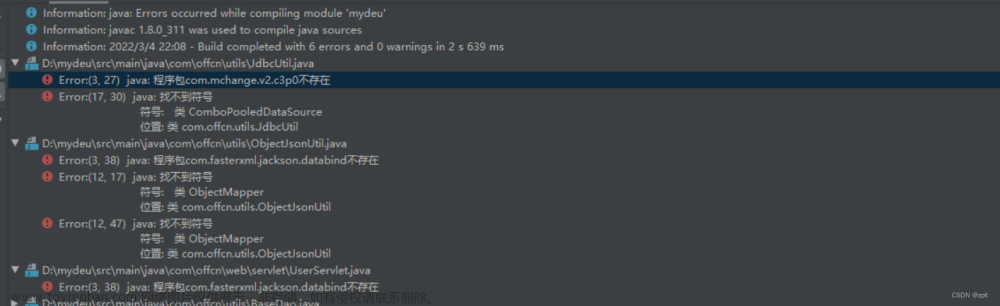

错误log:

报错路径分析:

该类型问题解决方法:

如何加物理约束?

最近跑工程,跑一个小时后place阶段报错,完整的错误截图:

错误log:

![Vivado2020.1 ERROR: [Place 30-681] Sub-optimal placement for a global clock-capable IO pin and MMCM](https://imgs.yssmx.com/Uploads/2023/05/451309-1.png)

翻译一下报错log:

全局时钟IO管脚和MMCM之间非最优布局。为了解决这错误,可在IO和MMCM之间插入BUFG。

IO锁定在IOB_X1Y132 (在SLR 0区域)

MMCM被时钟布局引擎暂时放置在MMCME3_ADV_X1Y5 (在SLR1区域)

log中的SLR为Super Logic Region,多个die用SLR编号区分。

两个die之间用SSI互联(Stacked Silicon Interconnect)。

报错路径分析:

![Vivado2020.1 ERROR: [Place 30-681] Sub-optimal placement for a global clock-capable IO pin and MMCM](https://imgs.yssmx.com/Uploads/2023/05/451309-2.png)

管脚输入rx_clk时钟经过IBUF直接接到MMCM。

现在布局结果 MMCM放置在 SLR1区域 MMCME3_ADV_X1Y5。

而pin 布局在SLR 0区域IOB_X1Y132。

可以看到从时钟pin到mmcm输入跨SLR,所以信号必须经过BUFG走全局时钟网络,否则就会报错。

该类型问题解决方法:

- log提到的修改代码,在pin与mmcm之间插入BUFG。

- 增加物理约束,把mmcm放置在SLR0 区域。

个人建议资源不冲突情况下用方法2 更方便,节省综合时间。

如何加物理约束?

首先我们打开综合网吧,ctrl+f 查找BELs类型,关键字输入MMCM,回车即可得到该FPGA所有MMCM资源,如下图

![Vivado2020.1 ERROR: [Place 30-681] Sub-optimal placement for a global clock-capable IO pin and MMCM](https://imgs.yssmx.com/Uploads/2023/05/451309-3.png)

![Vivado2020.1 ERROR: [Place 30-681] Sub-optimal placement for a global clock-capable IO pin and MMCM](https://imgs.yssmx.com/Uploads/2023/05/451309-4.png)

整个VU440 FPGA用clock region分区

X0Y0 -> X8Y14 一共9*15=135区域

其中

SLR0 :Y0 -> Y4

SLR1 :Y5 -> Y9

SLR2 :Y10 - Y14

MMCME3_ADV_X0Y14 对应时钟区域X0Y14

MMCME3_ADV_X1Y14 对应时钟区域X7Y14

一共2*15 = 30个MMCM资源

每个mmcm资源带两个PLLE3_ADV 一共60个PLL资源

通过网表我们查看输入时钟pin属于哪个时钟区域,可以设置对象高亮在device里面直接看到,如下图所示:

![Vivado2020.1 ERROR: [Place 30-681] Sub-optimal placement for a global clock-capable IO pin and MMCM](https://imgs.yssmx.com/Uploads/2023/05/451309-5.png)

rx_clk 输入pin用黄色标识,可以看到输入时钟管脚在时钟区域(clock region)X7Y2

管脚所在时钟区域X7Y2,该时钟区域里面包含一个MMCM,即MMCME3_ADV_X1Y2文章来源:https://www.toymoban.com/news/detail-451309.html

所以新增加以下约束即可:文章来源地址https://www.toymoban.com/news/detail-451309.html

set_property LOC MMCME3_ADV_X1Y2 [get_cells fpga_top/eth_wrapper/rx_clk_mmcm_inst/mmcme3_adv_inst]到了这里,关于Vivado2020.1 ERROR: [Place 30-681] Sub-optimal placement for a global clock-capable IO pin and MMCM的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![【Vivado】 [Place 30-574] 时钟使用普通IO时的报错解决办法](https://imgs.yssmx.com/Uploads/2024/02/506736-1.png)

![Vivado报错[place 30-484] The packing of LUTRAM/SRL instance](https://imgs.yssmx.com/Uploads/2024/02/648571-1.png)

![vivado 错误提示[DRC REQP-21] 以及 vivado design initialization error](https://imgs.yssmx.com/Uploads/2024/02/738011-1.png)