实验四:智力抢答器预习报告

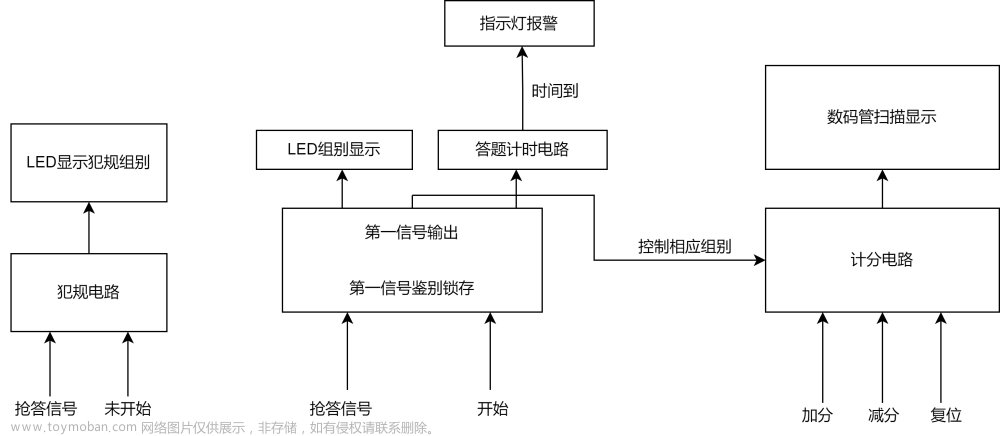

-------用D触发器74LS74设计制作一个四人智力竞赛抢答器电路

预习要求:

预习要点:

1、复习D触发器有关知识,写出其状态方程。双D触发器74LS74各引脚排列及引脚功能,使能端如何处理?如何测试触发器74LS74逻辑功能好坏?(结合D触发器一节和抢答器一节预习),画出74LS175逻辑符号和管脚功能。

2、参考图3.6.1 ,画出设计原理图(实验箱将提供一个连续的脉冲源)。说明设计原理:A.抢答装置如何鉴别第一信号?B.第一信号出现时如何屏蔽第二及以后的信号出现?C. 如何利用使能端整体清零控制?D.连续脉冲用多少HZ ? 能否用1HZ ?

(为了简化接线,具体实验时用74HC175)

预实验报告:

1.复习D触发器有关知识,写出其状态方程。双D触发器74LS74各引脚排列及引脚功能,使能端如何处理?如何测试触发器74LS74逻辑功能好坏?(结合D触发器一节和抢答器一节预习),画出74LS175逻辑符号和管脚功能。

1)D触发器状态方程 Q*=D

2)74LS74引脚排列及引脚功能

1D,2D输入信号

1CP,2CP输入脉冲信号

1Rd‘,2Rd’,1Sd‘,2Sd’复位端

1Q',1Q,2Q',2Q输出信号

Rd‘=Sd’=1

使能端接高电平

3)测试触发器74LS74逻辑功能

4)画出74LS175逻辑符号和管脚功能

2、参考图3.6.1 ,画出设计原理图(实验箱将提供一个连续的脉冲源)。说明设计原理:A.抢答装置如何鉴别第一信号?B.第一信号出现时如何屏蔽第二及以后的信号出现?C. 如何利用使能端整体清零控制?D.连续脉冲用多少HZ ? 能否用1HZ ?

A.B:在抢答之前,k1,k2,k3,k4开关接地,Q1~Q4=0。主持人清除信号,按下开关S又打开。当主持人宣布开始抢答后,若K1第一个按开关,则D1=1使Q1=1,Q1'=0,使1号与非门输出为1,经2号与非变为0,使3号与门输出恒为1,cp=1时,输入信号被封锁,从而屏蔽第二及以后的信号出现。

C:Rd‘的开关打开,Rd’=1,芯片不受使能端控制;Rd‘的开关闭合,Rd’=0,使输出信号全部为0.文章来源:https://www.toymoban.com/news/detail-451461.html

D:1khz左右,不可以用1hz文章来源地址https://www.toymoban.com/news/detail-451461.html

到了这里,关于数字电路实验四:智力抢答器预实验报告的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!