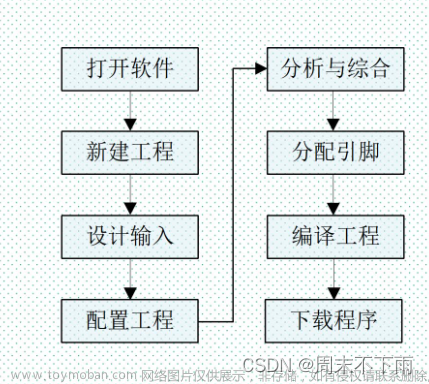

好久没有用VHDL写东西了,今天需要完成一个项目,重新复习一下

新建工程

新建工程

file-->New Project Wizard,

next, 选择存放的路径+名字(project+top-level 名字要相同),

next,File name名字同上,

next,选择响应的硬件,若只用于仿真不需要硬件的话,就默认

新建VHDL文件

文件名同工程名,编写代码,文件保存在工程中。

此次简单写了一个D触发器的代码,为了验证新安装的软件是有有问题。

-- D trigger achievement

library ieee;

use ieee.std_logic_1164.all;

ENTITY Dtrigger IS PORT(

D, clk : IN STD_LOGIC;

Q : OUT STD_LOGIC

);

END ENTITY Dtrigger;

ARCHITECTURE one of Dtrigger is

SIGNAL sig_save : STD_LOGIC;

BEGIN

PROCESS(clk)

BEGIN

if clk'event and clk='1' then

-- == rising_edge(clk) then

sig_save <= D;

end if;

END PROCESS;

Q <= sig_save;

END ARCHITECTURE one;

编译

点击编译按钮,若成功,说明软件安装过程没有问题;失败的话,根据提示,一一寻找解决问题的办法。

新建波形文件

为了进一步看一下我们这个器件是否成功,需要查看输入输出波形是否正确。

a. 新建

file-->new-->Verfication/Debugging Files-->University Program VWF

b. 设置

在Edit中选择End Time设置仿真终止时间,默认为1us,根据需要改,一般改大点

c. 在弹出界面中出现对应的这个波形文件

需要一些配置,我安装的Quartus默认使用的

点击clk, d,选择上面的波形,设置好波形;

在Simulation->Options-> 默认的为ModelSim,如果你的电脑没有安装ModelSim, 会无法使用。可以选Quartus II simulator

出现问题:ModelSim-Altera was not found. Please install ModelSim-Altera which is included with the Quartus II installer, or use the Quartus II Simulator instead by selecting "Simulation > Options > Quartus II Simulator"

选择Simulation > Options > Quartus II Simulator,点击运行

生成运行后的文件

结果文件,在时钟的上升沿变化信号。

查看硬件原理图

Tools下拉菜单里的Netlist Viewers–>RTL Viewer可以查看VHDL描述的硬件电路

出现的问题

Quartus II默认使用的是ModelSim-Altera,Simulation Waveform Editor默认为ModelSim。

ModelSim-Altera was not found. Please install ModelSim-Altera which is included with the Quartus II installer, or use the Quartus II Simulator instead by selecting "Simulation > Options > Quartus II Simulator"

解决这个问题:

a. 在Simulation Waveform Editor中设置Simulation->Options-> Quartus II simulator;use the Quartus II Simulator instead by selecting "Simulation > Options > Quartus II Simulator"

b.设置EDA Simulation Tool. 在Quartus中Assignments->Simulation->Tool name中选择ModelSim->Apply, 必须要点击Apply, 点击OK不会生效。 系统默认的为ModelSim-Altera。原因就在这里

复习语法

-- D trigger achievement

--库:数据的集合,内含各类包定义、实体、构造体等

library ieee; --VHDL的标准库的扩展

use ieee.std_logic_1164.all; --VHDL的标准库

-- 定义了一个实体, 格式

--Entity 实体名 IS

-- [类属参数说明]

-- [端口说明] --PORT(端口名1, 端口名N:方向:类型)

--End Entity

ENTITY Dtrigger IS PORT(

D, clk : IN STD_LOGIC;

Q : OUT STD_LOGIC

);

END ENTITY Dtrigger;

-- 构造体格式

-- Arcthitecture 构造体名 of 实体名 is

-- [定义语句] 内部信号、常数、元件、数据类型、函数等定义

-- begin

-- [并行处理语句和block、 process、function、procedure]

-- end 构造体名

ARCHITECTURE one of Dtrigger is

SIGNAL sig_save : STD_LOGIC;

BEGIN

PROCESS(clk)

BEGIN

if clk'event and clk='1' then

-- == rising_edge(clk) then

sig_save <= D;

end if;

END PROCESS;

Q <= sig_save;

END ARCHITECTURE one;Varible(变量),在程序中可以被赋值(:=),赋值后立即变化为新值;文章来源:https://www.toymoban.com/news/detail-452533.html

Signal(信号)在程序中可以赋值(<=),但不立即更新,当进程挂起后,才开始更新。文章来源地址https://www.toymoban.com/news/detail-452533.html

到了这里,关于Quartus II 的入门级使用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!