**

AXI_UART调试说明-PS使用AXI_Uartlite拓展PL端串口资源

**

注:本例程是在xc7z010clg400_1实现,若导入至复旦微电子需更改为xc7z045iffg900-2L

(目录中带*号的可略过)

背景:PS端UART资源有限,难以满足实际运用中多串口的需求。

具体方法:PS通过AXI总线调用PL的资源进行UART的拓展,本说明采用vivado自带的IP核AXI Uartlite完成,属于AXI_GPIO。

一、Vivado IP核建立

完成图如下

1.1 ZYNQ 核配置

这块一般默认即可(可以双机查看GP Master AXI Interface->M_AXI_GP0_Interface是否勾选);由于使用的是PL端的资源,AXI_Uartlite IP核实现串口收发功能,故PS端不用配置其它设置;

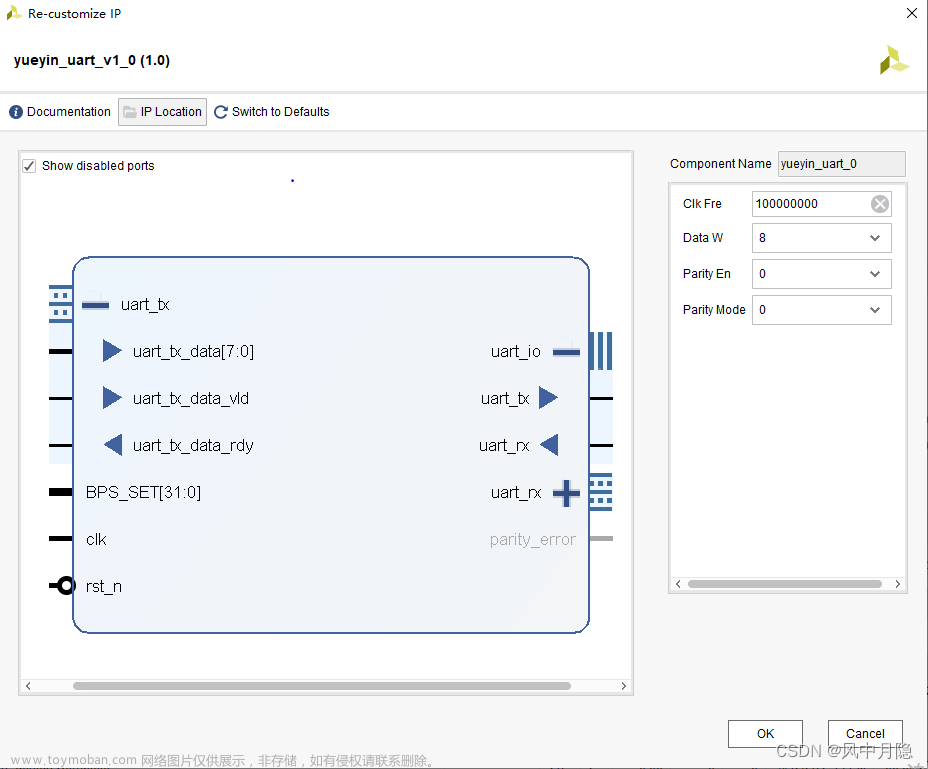

1.2 AXI_Uartlite IP核配置

注:此处配置时,时钟和波特率一旦配置好,再更改时需要重新生成顶层文件及比特流;

(1)观察.bd文件,AXI_Uartlite IP核右边的UART管脚,通过自动布线迁到uart_rtl_0;

(2)uart_rtl_0对应的是PL端所约束的任意两个管脚;

注:这里不必考虑这两个引脚是怎么牵出来能作为串口接收发送的,AXI_Uartlite IP核内部逻辑实现模拟串口收发功能,通过引出uart_rtl_0作为任意约束脚,达到串口通信的目的;

1.3 编译VIVADO FPGA工程

Step1:单击 Block 文件—>右键—>the Output ProductsGlobalGenerate。

Step2:单击 Block 文件—>右键—>Create a HDL wrapper(生成 HDL 顶层文件)Let vivado manager wrapper and auto-update(自动更新)。

Step3:生成 Bit 文件。

Step4:导出到硬件: File—>Export Hardware—>Include bitstream

加载 SDK:File—>Launch SDK—>OK

注:调用PL端时,导出硬件需勾选Include bitstream

1.4 新建VIVADO SDK工程

Step1:打开 SDK 后,只能看到如下一个工程

Step2: 需要手动创建一个 application 工程,模板选择 helloworld。输入工程名字,单击 Next。

选择Hello Word,创建一个包含Hello Word的工程,单击 Finish 完成创建。之后会自动生成一个与 Application 工程名字相同且带有_bsp 后缀的 bsp 工程。

点击 axi_uartlite IP 对应的 Import Examples 工程,可以导入 axi_uartlite 的测 试用例。这里导入 xuartlite_polled_example 工程。

至此,在 Xilinx Vivado 和 Xilinx SDK 的开发流程完成。接下来要转入 Procise 开发流程。

注意此处的 axi_uart_bsp 工程的存在非常重要(必须存在),其内部存放的是与 PL 的 Block Design 相关的 IP 的驱动程序,因为接下来的 Procise 软件里面的 From Vivado 操作,会搜索 Xilinx SDK 工程下面以“_bsp”结尾的文件夹,并拷贝此文件夹里面的驱 动到 Procise 工程 SDK 的 FM_QL_bsp 文件夹下的 pl 文件夹中 。否则 Procise 软件 From Vivado 操作后,导出的 IAR 工程,将没有 pl 部分的驱动目录。

*1.5 下载调试

Step1:点击Xilinx—>Program FPGA 烧写bit文件。

注:红框中system_wrapper.bit即为“Step4:导出到硬件: File—>Export Hardware—>Include bitstream”这步所生成的bit;

Step2:如下图绿色播放按钮烧写elf文件(在vivado sdk中烧写)。

注:此处第一次打开工程下载会弹出选择窗口,选择run as hardware即可

二、Procise From Vivado

Step1:导入Vivado工程

点击PSOC—>from vivado

导入所需的vivado文件.bd和.xci,(参考如下黄色高亮)

.bd路径为:

C:/Users/11/Desktop/aa/axi_uart1/axi_uart/axi_uart.srcs/sources_1/bd/system/system.bd.xci路径为:

C:/Users/11/Desktop/aa/axi_uart1/axi_uart/axi_uart.srcs/sources_1/bd/system/ip/system_processing_system7_0_0/system_processing_system7_0_0.xci

Step2:导出SDK

观察bsp,pl文件夹为PL端生成的各种IP核的库函数,这里主要说明uartlite_v3_2

(Procise 软件里面的 From Vivado 操作,会搜索 Xilinx SDK 工程下面以“_bsp”结尾的文件夹,并拷贝此文件夹里面的驱 动到 Procise 工程 SDK 的 FM_QL_bsp 文件夹下的 pl 文件夹中)

Include 文件中包含的是软件ip核的基本类型,适用于各种xilinx处理器

Xparameters.h 这个文件是pl端配置完各种IP核后,所在生成的各寄存器的基地址及其它宏定义(比如uartlite的波特率,数据位等),如下图所示:

对比下图发现,Xparameters.h 文件中 #define XPAR_UARTLITE_0_BASEADDR 的值刚好对应pl端配置寄存器RX_FIFO的值

Uartlite_v3_2文件中,包含共10个.c/.h文件,这些是从vivado工程中的pl端导入

(需手动添加)

注:添加.h文件后需要查看路径是否包含,以免编译报错

如下图中,可以看到路径包含pl内的include和libsrc

注:这里尽量使用相对路径,绝对路径受文件位置移动影响,需每次更改路径文章来源:https://www.toymoban.com/news/detail-452622.html

文章来源地址https://www.toymoban.com/news/detail-452622.html

文章来源地址https://www.toymoban.com/news/detail-452622.html

到了这里,关于AXI_UART调试说明-PS使用AXI_Uartlite拓展PL端串口资源的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!