第4关:16位快速加法器设计

实验目的

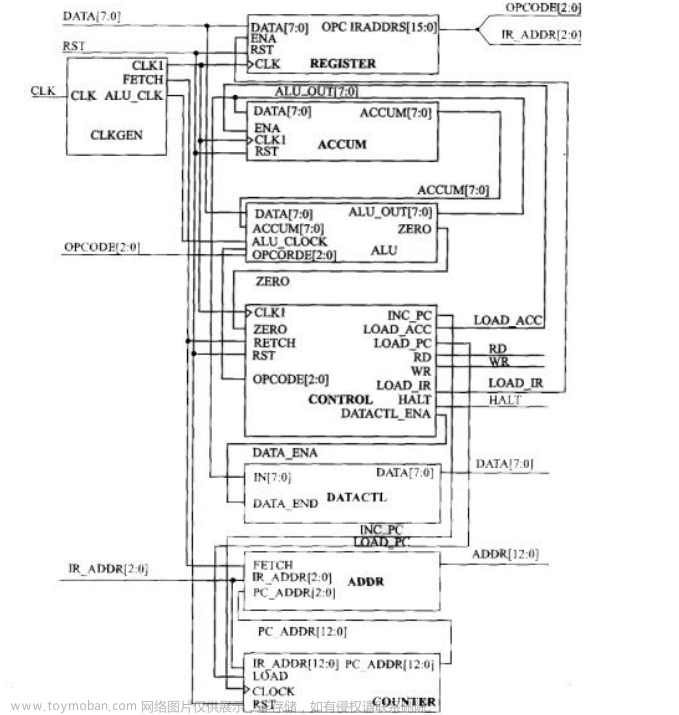

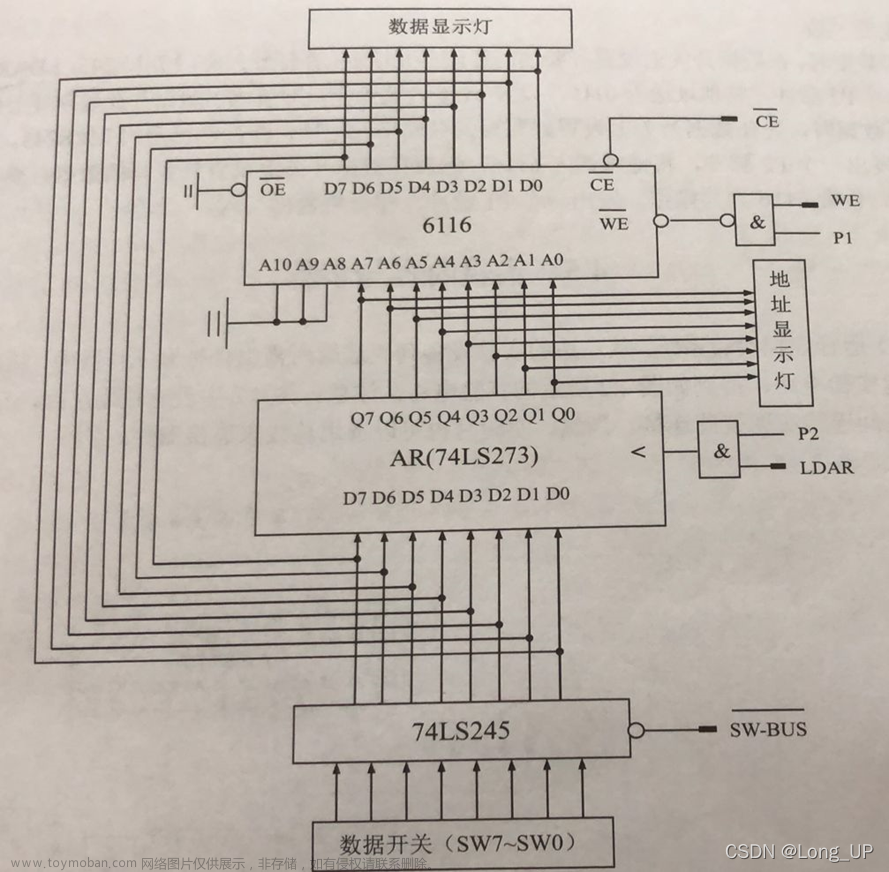

帮助学生理解成组进位产生函数,成组进位传递函数的概念,熟悉 Logisim 平台子电路的概念,能利用前述实验封装好的4位先行进位子电路以及4位快速加法器子电路构建16位、32位、64位快速加法器,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。

视频讲解

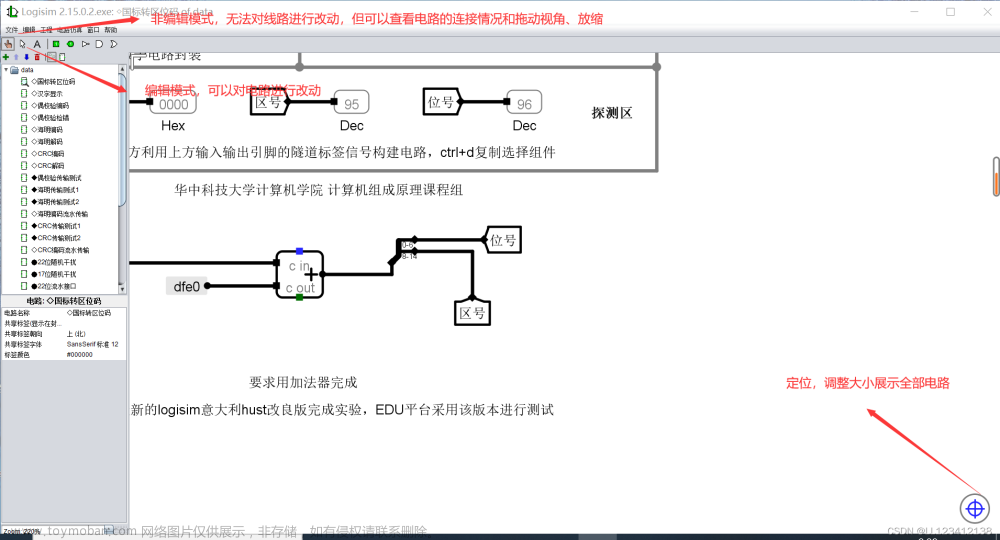

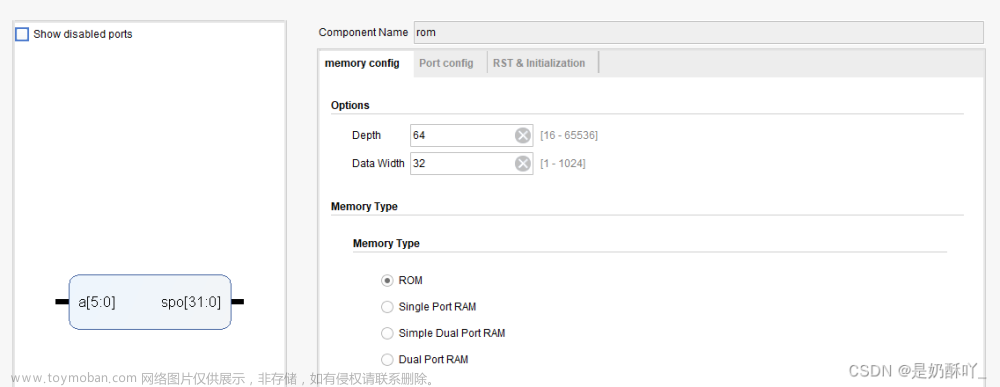

####实验内容 在 Logisim 中打开 alu.circ 文件,在对应的子电路中利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器,并验证其功能是否正常,快速加法器引脚定义如图所示。其中 X,Y 为16位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为16位成组进位生成函数和成组进位传递函数。

电路框架

alu.circ

电路引脚

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| X | 输入 | 16 位 | 加数 |

| Y | 输入 | 16 位 | 加数 |

| C0 | 输入 | 1 位 | 进位输入 |

| S | 输出 | 16 位 | 运算和 |

| C16 | 输出 | 1 位 | 最 16 位进位位 |

| C15 | 输出 | 1 位 | 第 15 位进位位 |

| G* | 输出 | 1 位 | 成组生成函数 |

| P* | 输出 | 1 位 | 成组传递函数 |

电路测试

完成实验后,利用文本编辑工具打开 alu.circ 文件,将所有文字信息复制粘贴到 Educoder 平台的 alu.circ 文件中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

Cnt X Y C0 Sum G P C16 C1500 8001 0005 0 8006 0 0 0 001 2ece ea08 1 18d7 1 0 1 102 c8df e0e1 1 a9c1 1 0 1 103 9591 d843 0 6dd4 1 0 1 004 2f12 3a2a 0 693c 0 0 0 005 ba6a b8da 1 7345 1 0 1 006 cb1c 9d86 0 68a2 1 0 1 007 4649 fad8 0 4121 1 0 1 108 bc08 4570 0 0178 1 0 1 109 3a12 d42b 0 0e3d 1 0 1 1...

常见调试问题

为什么左右两边的内容完全一致,还判我错啊!

显示窗口没有显示完整,左右移动一下就会发现不一样的地方了。

开始你的闯关任务吧,升级打怪中....

参考答案:

直接复制代码,字数太多,发不了,后续会上传文件

参考电路图

如果对你有所帮助,感谢点赞加收藏!

完整的代码可以到【WRITE-BUG数字空间】我的个人学习圈查看。

附上链接:文章来源:https://www.toymoban.com/news/detail-453072.html

https://www.writebug.com/article/d06cb88a-f626-11ed-ada1-0242ac1a0006https://www.writebug.com/article/d06cb88a-f626-11ed-ada1-0242ac1a0006文章来源地址https://www.toymoban.com/news/detail-453072.html

到了这里,关于头歌计算机组成原理实验—运算器设计(4)第4关:16位快速加法器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!