实验目的

学生了解 MIPS \text{MIPS} MIPS 寄存器文件基本概念,进一步熟悉多路选择器、译码器、解复用器等 Logisim \text{Logisim} Logisim 组件的使用,并利用相关组件构建 MIPS \text{MIPS} MIPS 寄存器文件。

主要任务

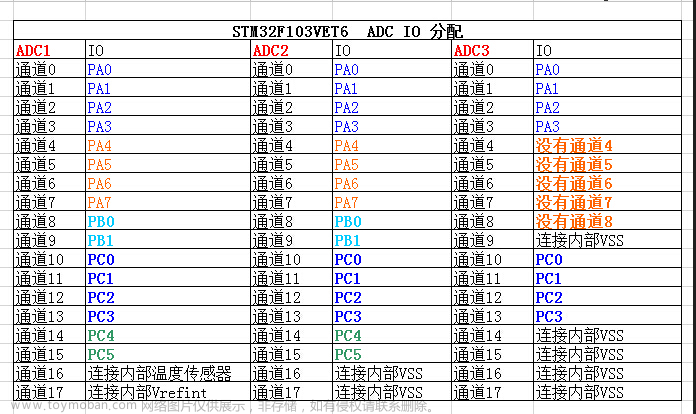

利用 Logisim \text{Logisim} Logisim 平台构建一个简化的MIPS寄存器文件,内部包含 4 4 4 个 32 32 32 位寄存器。 R 1 # R_1\# R1# 为第 1 1 1 个读寄存器的编号, R 2 # R_2\# R2# 为第 2 2 2 个读寄存器的编号。 W # W\# W# 为写入寄存器编号, D i n Din Din 为写入数据, W E WE WE 写使能信号,为 1 1 1 时在 C L K CLK CLK 上跳沿将 D i n Din Din 数据写入 W # W\# W# 寄存器。 C L K CLK CLK 为时钟信号,上跳沿有效。 R D 1 RD_1 RD1 为 R 1 # R_1\# R1# 寄存器的值, R D 2 RD_2 RD2 为 R 2 # R_2\# R2# 寄存器的值, MIPS \text{MIPS} MIPS 寄存器文件中 0 0 0 号寄存器的值恒零。

实验原理

W

#

W\#

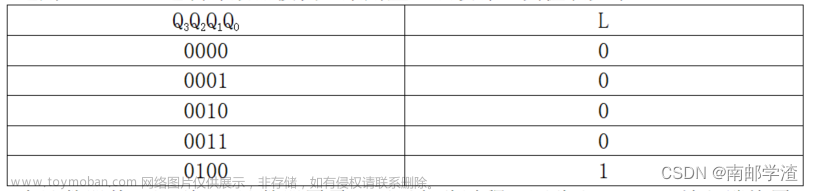

W# 通过译码器后,可得到写入寄存器编号,连接写入寄存器的一端成为高电平。

对于一个编号为

X

X

X 的寄存器,当且仅当写使能信号为

1

1

1 且写入寄存器编号为

X

X

X 时,该寄存器允许写入,可以此作为寄存器不忽略信号的标志。

由于

0

0

0 号寄存器的值恒零,因此

0

0

0 号寄存器输入端为常量

0

0

0,其余寄存器输入端为

D

i

n

Din

Din。

为得到

R

D

1

RD_1

RD1,可将所有寄存器的输出信号输入多路选择器,根据读寄存器编号

R

1

#

R_1\#

R1# 选择一个结果输出;同理可得到

R

D

2

RD_2

RD2。文章来源:https://www.toymoban.com/news/detail-454416.html

电路图

文章来源地址https://www.toymoban.com/news/detail-454416.html

文章来源地址https://www.toymoban.com/news/detail-454416.html

到了这里,关于MIPS寄存器文件设计实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!