目录

一、理论基础

二、核心程序

三、测试结果

一、理论基础

Sigma-Delta ADC是一种目前使用最为普遍的高精度ADC结构,在精度达到20位以上的场合,Sigma-Delta是必选的结构。通过采用过采样、噪声整形以及数字滤波技术,降低对模拟电路的设计要求,实现了其他类型的ADC无法达到的高精度和低功耗。通常情形下,各种类型ADC的精度与速度关系如图1所示。

Sigma-Delta ADC的运作过程,就是把待测信号Vin与参考电压(±Vref)之间的差值进行不断的累积并通过反馈令这个差值趋于零。

实质上ADC就是除法器。

Dout=(Vin/Vref) * 2^n

一个分辨率为n位的ADC完成了一个以Vref为除数的除法,并且把结果用n位二进制数来表达。

那么什么是Sigma-Delta ADC?

Sigma-Delta最终实现的,与所有的ADC一样,就是完成除法。模拟集成电路中除法器是不可实现的,但是模拟电路可以非常好的实现加法和减法(用运放及模拟开关对电容进行充放电)。Sigma-Delta ADC正是用加法和减法去实现除法的一种方式。

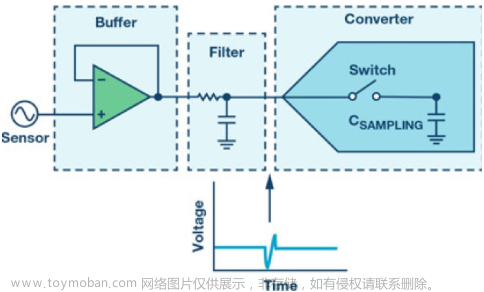

具体来说,如图2所示,Delta-Sigma ADC的工作原理是由差动器、积分器和比较器构成调制器,它们一起构成一个反馈环路。调制器以大大高于模拟输入信号带宽的速率运行,以便提供过采样。模拟输入与反馈信号(误差信号)进行差动(delta)比较。该比较产生的差动输出馈送到积分器(sigma)中。然后将积分器的输出馈送到比较器中。比较器的输出同时将反馈信号(误差信号)传送到差动器,而自身被馈送到数字滤波器中。

系统分为两个部分,

第一部分是sigma delta ADC把接收天线接收的交流信号转化成数字信号。

输入频域因为是AM信号,所以在5K~2M HZ之间,ADC的精度要求不限,能满足一般音频处理即可(满足演示要求,建议采样64MHZ上限,8位)此部分设计需要用到FPGA开发板上的2个LVDS输入端口。 此部分ADC分为两个部分modulator和decimator。

第二部分输入为第一部分的数字输出信号,进行一般的软件无线电设计即可。按照一般收音机的设计,将硬件全部由软件(FPGA)来替代。收音机的挑台旋转按钮可用开发板上的开关来设计。

二、核心程序

`timescale 1 ns / 1 ns

module tops(

i_clk,

i_rst,

i_ADC,

i_sel,

i_adjust1,

i_adjust2,

o_ADCLK2,

o_DACLK2,

o_DAC

);

input i_clk;

input i_rst;

input signed[9:0] i_ADC;

input i_sel;

input i_adjust1;

input i_adjust2;

output o_ADCLK2;

output o_DACLK2;

output signed[9:0]o_DAC;

wire CLK2;

pllclk2 pllclk2_u(

.areset (i_rst),

.inclk0 (i_clk),

.c0 (o_ADCLK2),

.c1 (CLK2),

.locked ()

);

assign o_DACLK2 = ~CLK2;

wire signed[7:0]tmps;

AMdemods AMdemods_u(

.i_clk (CLK2),

.i_rst (i_rst),

.i_din (i_ADC[9:2]),

.i_sel (i_sel),

.i_adjust1 (i_adjust1),

.i_adjust2 (i_adjust2),

.o_am (),

.o_dout (tmps)

);

assign o_DAC = {tmps[7],tmps[7],tmps};

endmodule

A01-120

`timescale 1 ns / 1 ns

module am_signal(

i_clk,

i_rst,

o_dout

);

parameter NN = 22949673;

parameter NN2 = 22949673*20;

parameter AM = 1;

input i_clk;

input i_rst;

output signed[7:0]o_dout;

wire signed[9:0]o_fsin;

wire signed[9:0]o_fcos;

nco_ip nco_ip_u1(

.phi_inc_i (NN),

.clk (i_clk),

.reset_n (~i_rst),

.clken (1'b1),

.fsin_o (o_fsin),

.fcos_o (o_fcos),

.out_valid ()

);

wire signed[9:0]o_fsin2;

wire signed[9:0]o_fcos2;

nco_ip nco_ip_u2(

.phi_inc_i (NN2),

.clk (i_clk),

.reset_n (~i_rst),

.clken (1'b1),

.fsin_o (o_fsin2),

.fcos_o (o_fcos2),

.out_valid ()

);

reg signed[19:0]tmps;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

tmps <= 20'd0;

end

else begin

tmps <= o_fsin * o_fcos2;

end

end

assign o_dout = tmps[18:11];

endmodule `timescale 1 ns / 1 ns

module AMdemods(

i_clk,

i_rst,

i_din,

i_sel,

i_adjust1,

i_adjust2,

o_am,

o_dout

);

parameter NN2 = 22949673*20;

input i_clk;

input i_rst;

input signed[7:0] i_din;

input i_sel;

input i_adjust1;

input i_adjust2;

output signed[7:0]o_am;

output signed[7:0]o_dout;

reg signed[7:0]tmps;

am_signal am_signal_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_dout(o_am)

);

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

tmps <= 8'd0;

end

else begin

if(i_sel == 1'b1)

tmps <= o_am;

else

tmps <= i_din;

end

end

//AM demodulation

reg[31:0]PHASE;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

PHASE <= NN2;

end

else begin

if(i_adjust1 == 1'b1)

PHASE <= NN2 + 32'd1;

else

PHASE <= PHASE;

if(i_adjust2 == 1'b1)

PHASE <= NN2 - 32'd1;

else

PHASE <= PHASE;

end

end

wire signed[9:0]o_fsin;

wire signed[9:0]o_fcos;

nco_ip nco_ip_u(

.phi_inc_i (PHASE),

.clk (i_clk),

.reset_n (~i_rst),

.clken (1'b1),

.fsin_o (o_fsin),

.fcos_o (o_fcos),

.out_valid ()

);

reg signed[17:0]tmps2;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

tmps2 <= 18'd0;

end

else begin

tmps2 <= tmps * o_fcos;

end

end

filter filter_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (tmps2[16:9]),

.o_dout(o_dout)

);

endmodule 三、测试结果

首先使用MATLAB对AM收音机的基本功能进行验证

下面我们主要介绍FPGA部分,FPGA部分分为三个部分:

这里,我们主要基于DE0开发板进行设计,下面首先分析一下DE0开发板。

整个系统的接口含义如下所示:

表一、顶层模块接口定义

| 名称 |

位宽 |

方向 |

描述 |

备注 |

| I_clk |

1 |

输入 |

时钟 |

上升沿有效,频率为开发板的晶振 |

| I_rst |

1 |

输入 |

复位 |

单周期低电平有效,下降沿有效 |

| I_ADC |

10 |

输入 |

A/D采样数据 |

有符号二进制 |

| O_ADCLK2 |

1 |

输出 |

A/D采样时钟 |

|

| O_DACLK2 |

1 |

输出 |

D/A采样时钟 |

|

| O_DAC |

12 |

输出 |

D/A采样数据 |

偏移二进制 |

管脚分配如下所示:

文章来源:https://www.toymoban.com/news/detail-454761.html

文章来源:https://www.toymoban.com/news/detail-454761.html

文章来源地址https://www.toymoban.com/news/detail-454761.html

文章来源地址https://www.toymoban.com/news/detail-454761.html

到了这里,关于基于FPGA的sigma delta ADC软件无线电设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!