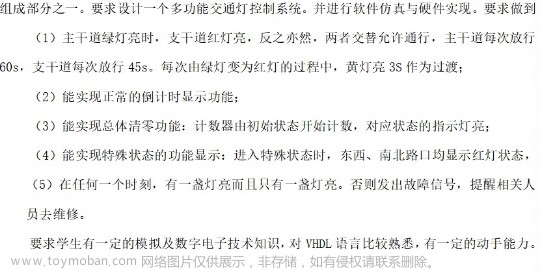

一、功能

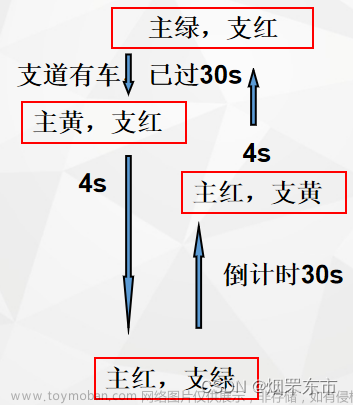

二、状态分析

三、verilog实现

用三段式状态机实现交通灯电路,设计和TB代码如下:

// Design Name: traffic_light

// Module Name: traffic_light

// Description: ↓ ↓ ↓

// Create Date: 2022/3/28

/*

state:

s0: main-green, branch-red, when x=1 s0->s1

s1: main-yellow, branch-red, delay s1->s2

s2: main-red, branch-red, delay s2->s3

s3: main-red, branch-green, when x=0 s3->s4

s4: main-red, branch-yellow, delay s4->s1

port:

input: clk,rst_n,x

output: main, branch

*/

`timescale 1ns / 1ps

module traffic_light(

input clk,

input rst_n,

input x,

output reg [1:0] main,

output reg [1:0] branch

);

parameter green = 2'd1,

yellow = 2'd2,

red = 2'd3;

parameter s0 = 3'd0,

s1 = 3'd1,

s2 = 3'd2,

s3 = 3'd3,

s4 = 3'd4;

reg [3:0] state;

reg [3:0] next_state;

//state transfer

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

state <= s0;

else

state <= next_state;

end

//transfer logic

always @(*)begin

case(state)

s0: next_state = x ? s1 : s0;

s1: #600 next_state = s2;

s2: #600 next_state = s3;

s3: next_state = x ? s3 : s4;

s4: #600 next_state = s0;

default: next_state = state;

endcase

end

//output

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

main <= green;

branch <= red;

end

else begin

case(state)

s0: begin main <= green; branch <= red; end

s1: begin main <= yellow; branch <= red; end

s2: begin main <= red; branch <= red; end

s3: begin main <= red; branch <= green; end

s4: begin main <= red; branch <= yellow; end

default: begin main <= green; branch <= red; end

endcase

end

end

endmodule

testbench:

`timescale 1ns / 1ps

module tb_traffic_light();

parameter period = 10; //100mhz

reg clk;

reg rst_n;

reg x;

wire [1:0] main;

wire [1:0] branch;

always #(period/2) clk = ~clk;

initial begin

clk = 1'b0;

rst_n = 1'b0;

x = 0;

#60

rst_n = 1'b1;

#1234

x = 1;

#1234

x = 0;

end

traffic_light u_traffic_light(clk,rst_n,x,main,branch);

endmodule

四、仿真&综合

仿真结果:

综合结果:文章来源:https://www.toymoban.com/news/detail-455412.html

综合结果:文章来源:https://www.toymoban.com/news/detail-455412.html

文章来源地址https://www.toymoban.com/news/detail-455412.html

文章来源地址https://www.toymoban.com/news/detail-455412.html

到了这里,关于交通灯电路及verilog实现(状态机)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!