不同的FPGA种类,配置的方式可能有稍许的差别。此处我们主要以7系列中XC7A200TFBG676为例,讲解FPGA的主要配置引脚。

1 简介

工具制程工艺的不同,FPGA主要可以分为16nm、20nm、28nm。不停的制程工艺下,有不同的产品,详细将下:

2 BANK 介绍

在FPGA的设计过程中,将FPGA的IO口划分为不同的BANK,常见的BANK有HP BANK、HR BANK、HD BANK。

| BANK |

HR BANKA |

HP BANK |

HD BANK |

| 全称 |

High Range |

High Performance |

High Desity |

| 电压范围 |

1.2~3.3V |

1.0~1.8V |

1.2~3.3V |

| 接口速率 |

以类型有关 |

支持高速接口 |

支持低速接口 |

| IO PIN数 |

50 |

52 |

24 |

| 差分对数 |

24 |

24 |

12 |

特别地,FPGA的配置关键一般均处于BANK0。

3 配置管脚说明

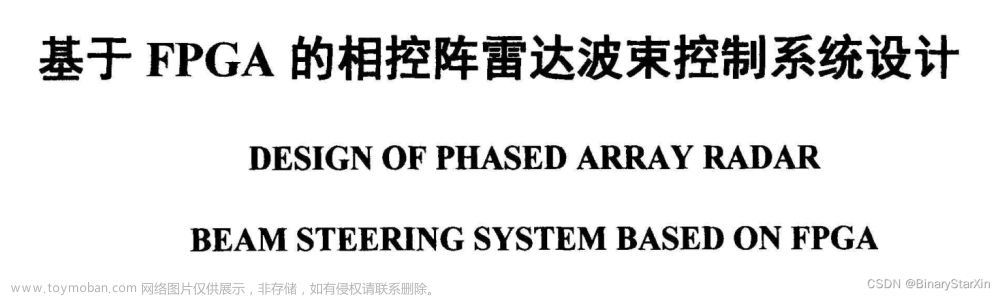

BANK0配置的引脚如下图所示:

接下来,分别对每个配置引脚做详细的说明

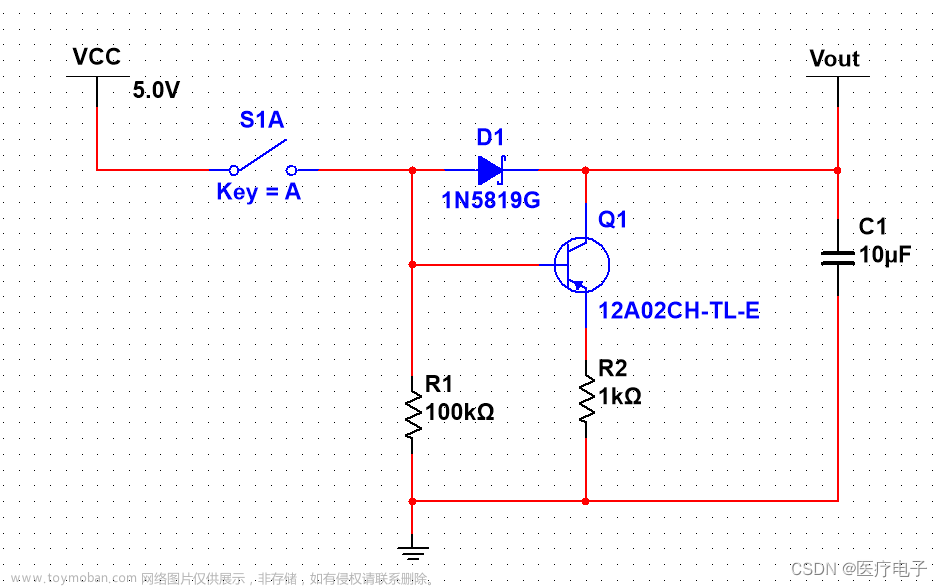

3.1 DXP与DXN配置

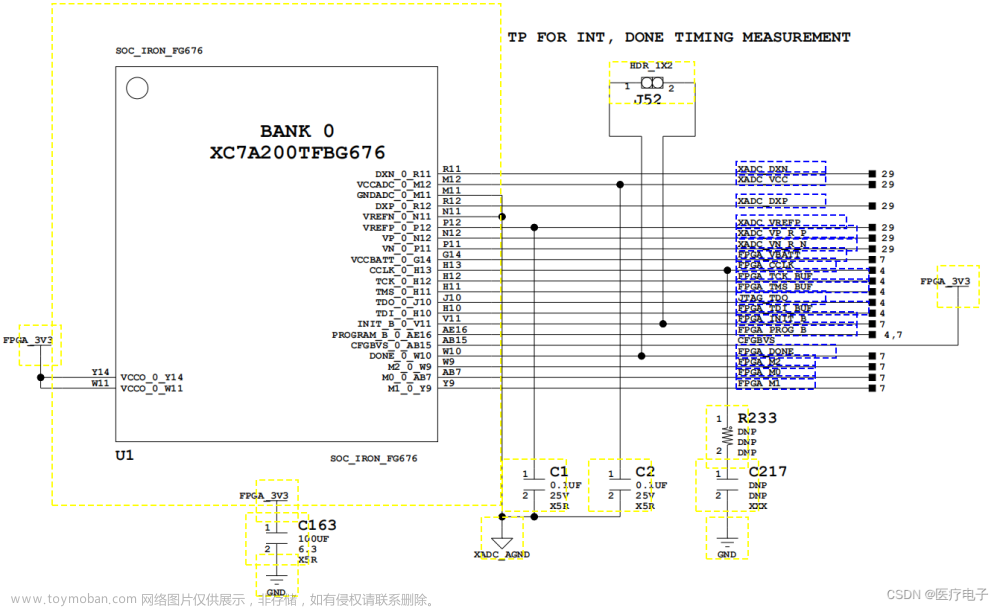

DXP、DXN 热敏二极管温度传感器引脚,在BANK0热二极管被允许接入使用DXP和DXN引脚,当不使用时,连GND。在设计该部分电路时,可以使用MAX6642替代热敏二极管。大多数热敏二极管温度传感器,包括MAX1617和MAX6654,与二极管都有两个连接点:DXP和DXN。DXP连接至热敏二极管的阳极,源出二极管偏置电流。DXN吸入偏置电流,并将阴极偏置在0.7V左右。具体的连接方式见下图:

MAX6642只有一个DXP端,与热敏二极管的阳极相连,该器件没有DXN端,而是将阴极直接与地相连。这就需要对电路板做出一些修改,如图2所示。注意,GND同时用作电源地和阴极连接,因此热敏二极管的阴极需在图2所示MAX6642处接地。热敏二极管与MAX6642之间不应有其它与地相连的引线,因为地电流通过引线将产生小的电压降,直接影响温度测量精度。具体的连接方式见下图:

3.2 VCCADC配置

XADC的工作电源为1.8V,第二个是XADC的采样参考电压,VREFP VREFN两个引脚,为了简化硬件设计,此处采用内部参考电压,所以两个引脚均需接地。

3.3 VP和VN配置

-

VRN 这个引脚针对DCI电压的N晶体管参考电阻,每个bank,用一个10K的电阻拉高。

-

VRP 这个引脚针对DCI电压的P晶体管参考电阻,每个bank,用一个10K的电阻拉低。

3.4 VCCBATT

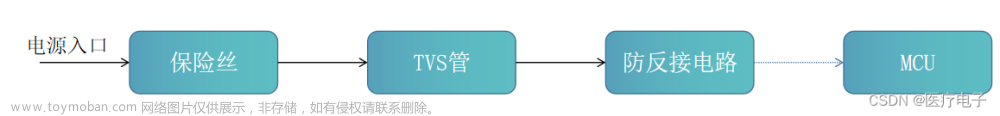

VCCBATT是FPGA内部易失性存储器的电池备份电源,用于存储AES解密器的密钥。 对于需要来自易失性密钥存储区的解密密钥的加密比特流,将此引脚连接到电池以在FPGA未供电时保留密钥。 如果不要求使用易失性密钥存储区中的解密密钥,请将此引脚连接到GND或VCCAUX。 引脚名称包含“_0”存储区标识,但它不是I / O,不受VCCO_0的影响。官方电路如下:

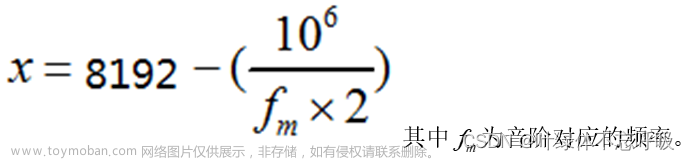

3.5 配置模式

常见的配置模式主要有七种,分别是主串配置模式、主SelectMAP配置模式、主SPI FLASH配置模式、主BPI FLASH配置模式、从串配置模式、从SelectMAP配置模式、JTAG配置模式。配置工作模式我们只需要配置M[2:0]即可,具体的配置方式如下:文章来源:https://www.toymoban.com/news/detail-455782.html

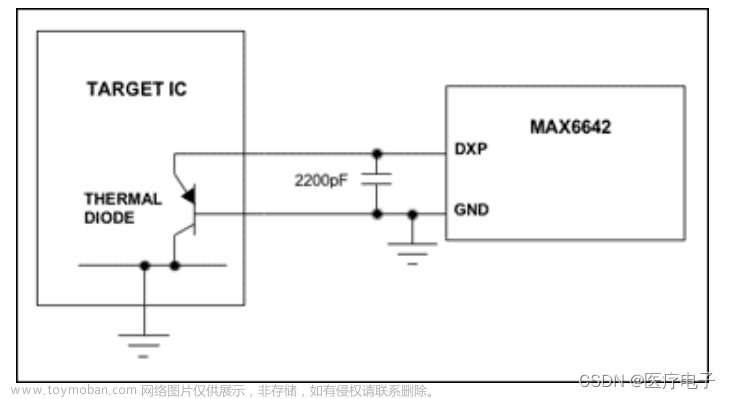

关于FPGA的配置模式,我们一般使用主SPI比较常见,此处我们针对这种模式进行分析:文章来源地址https://www.toymoban.com/news/detail-455782.html

到了这里,关于数字电路硬件设计系列(六)之FPGA配置引脚的设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!