1、GD32F4以太网简介

GD32F4系列以太网模块包含10/100Mbps以太网MAC,数据的收发都通过DMA进行操作,支持MII(媒体独立接口)与RMII(简化的媒体独立接口)两种与物理层(PHY)通讯的标准接口。

2、以太网模框图简介

以太网需要外接一个PHY(以太网芯片)才可以进行通信。与PHY连接的方式有两种,一种是通过MII直接连接,将MII接口化简为RMII接口,然后再与PHY进行连接。另外与PHY相连的还有一个SMI接口(站点管理接口)用于配置和管理PHY芯片。

AHB仲裁,在当TXDMA与RXDMA同时需要访问AHB总线的时候起作用。因为以太网外设与AHB的接口只有一个,所以当收发两个模块都需要访问AHB总线的时候就有一个优先级的问题。仲裁的方式有两种,一种是固定优先级,RXDMA总是对总线有更高优先级访问权限,一种是轮询优先级,TXDMA和RXDMA按照一定的访问比例来轮流访问总线,例如设置比例为2:1,但是目前这个比例表示什么还不太清楚,是RXDMA和TXDMA对总线的总访问次数的比值,还是发生竞争总次数中,RXDMA和TXDMA优先访问次数的比值,又或者是其他。

TXDMA控制器,用于从从内存中读取描述符和数据,并将状态写入到内存中。

TxMTL内含TxFIFO,用于缓存待MAC发 送的数据。

TXMAC控制数据帧的发送。

RxDMA控制器,用于从内存中读取描述符,以及将接收数据与状态写入内存中。

RxMTL内含RxFIFO与TXFIFO是相互独立的,用于缓存接受到的数据。

RXMAC控制数据接收,有过滤功能。

3、以太网主要模块介绍

SMI接口

SMI用于访问和配置PHY芯片中的寄存器。由两根线组成,MDC时钟线和MDIO数据线。SMI主要用到两个寄存器ENET_MAC_PHY_DATA和ENET_MAC_PHY_CTL。ENET_MAC_PHY_DATA中,在写数据时存放的是待写的数据;在读数据是存放的是读到的数据。ENET_MAC_PHY_CTL中PA存放的是PHY的地址;PR中存放的是待访问的PHY的寄存器;PW控制读写,0为读操作,1为写操作;PB用于判断传输状态,PB由软件置1,开始读或者写操作,当读或者写完成后,会又硬件清零。

RMII接口与MII接口

SYSCFG_CFG1寄存器的第23位ENET_PHY_SEL位进行配置,选择使用MII或者RMII模式,默认为MII模式。

DMA控制器

这里说的DMA是以太网模块中的专用DMA。在发送数据的时候,CPU将数据打包好,存放与内存中,DMA控制器控制通过DMA将内存中的数据发送至TXFIFO中等待发送。在数据接收的时候,DMA控制器通过DMA将RXFIFO中的数据搬运至内存中,然后通知CPU。这个DMA与CPU之间的数据交换通过寄存器和描述符列表来控制。寄存器,很好理解,就是用来配置DMA、查看的DMA状态的,是芯片外设自带的。**至于描述符列表,这个是我们用户自己申请的一个内存。你可以把描述符理解为一个结构体,这个结构体里的成员用来描述一段内存,包括了内存的地址、长度等信息。而被描述的这段内存就是用来存储待发送的数据或者待接收的数据。描述符列表就是多个描述符连在一起组成的一个表。这个表的结构有两种,一种是链结构(链表),一种是环结构(环形缓存区)。**结构如下图:

一般有两个描述符队列,一个用作发送,一个用作接收。当 DFM位为 0时(常规描述符),发送描述符由四个描述符字 TDES0-TDES3组成,也就是我们的结构体只有4个成员,当 DFM位为 1时,发送描述符由 8个描述符字 TDES0-TDES7组成(增强描述符),也就是我们的结构体有8个成员。同样的,当 DFM位为 0时,接收描述符由四个描述符字 RDES0-RDES3组成,当 DFM位为 1时,接收描述符由 8个描述符字 RDES0-RDES7组成。描述符的结构如下图所示

常规TXDMA描述符

增强TXDMA发送描述符

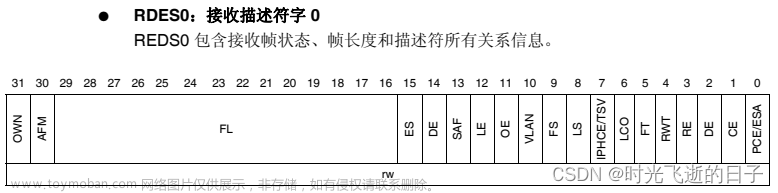

常规RXDMA描述符

增强RXDMA描述符

在常规描述符,如果描述符列表的结构为链结构,那么TDES和RDES3中的内容为下一个描述符的地址,如果是环结构,则存放的是缓存区2的地址,因此当描述符列表的结构为链结构的时候,一个描述符对应一个缓存;如果描述符结构是环结构的时候,一个描述符对应两个缓存。

在创建完描述符列表后,需要将描述符列表的首地址存储在相应寄存器中,DMA通过首地址一个一个去查看描述符。对于环结构的描述符列表,描述符的地址关系如下:

下个描述符地址 = 当前描述符地址 + 16 + DPSL * 4 这是常规描述符

下个描述符地址 = 当前描述符地址 + 32 + DPSL * 4 这是增强描述符

DPSL表示描述符跳跃长度,也就是两个描述符之间的间隔,一般都是相邻的,值为0,在ENET_DMA_BCTL中设置。

发送帧处理:发送数据时,CPU需要将发送数据打包封装成以太网数据帧,放置在缓存区;然后设置TXDMA的描述符,在TDES0中,一般需要设置FSG、LSG,这两个表示帧头与帧尾,因为有时候设置的缓存区太小,一个缓存区存不下一帧数据,数据就会被分散在多个缓存区中,FSG置位,表示当前描述符指向的缓存帧为帧头,LSG置为表示当前描述符指向的缓存帧为帧尾。一般我们设置的缓存帧都是足够大的(一帧以太网数据需要的缓存大概1518左右,不同标准可能有些差别),所以FSG、LSG会同时置位。CPU将描述符TDES0的DAV位为1,DMA查询到DAV为1,就将数据传输到TXFIFO中进行发送;如果查询的描述符中DAV为0,则说明数据还没准备好,DMA会先挂起,发送的时候需要软件向ENET_DMA_TPEN中写入任意数据恢复DMA。

接收帧处理:接收数据时,RXDMA会将RDES0中的FDES和LDES置位,表示一帧的帧头和帧尾,一般我们申请的缓存大小都可以完整的存储一个以太网帧的数据,所以FDES和LDES同时置位。RXDMA将RDES0的 DAV置0,表示CPU可以对该描述符所指向的地址进行操作。ENET_DMA_STAT寄存器中的 RS位将置位,如果使能了接收中断,则会触发中断,用户可以在通过中断来读取相应的数据。当接收到一个新的数据时,如果描述符的 DAV位为 ’ 则 DMA控制器进入挂起状态,需要软件向ENET_DMA_RPEN中写入任意数据恢复DMA。

4、以太网配置流程

- 使能以太网时钟(HCLK、以太网收发时钟)

- 配置通讯接口:配置 SYSCFG模块,选择接口模式 MII或 RMII,配置GPIO

- 等待复位完成:轮询ENET_DMA_BCTL寄存器直到 SWR位复位( SWR位在上电复位后或系统复位后默认置位) 。

- 获取并配置 PHY寄存器参数(如全双工、半双工、速率等),速度等等)。根据外部 PHY支持的模式,配置ENET_MAC_CFG寄存器使与 PHY寄存器信息一致 。

- 初始化以太网的DMA模块,完成 DMA模块初始化。

- 初始化用于存放描述符列表以及数据缓存的物理内存空间,将列表首地址写入ENET_DMA_RDTADDR和 ENET_DMA_TDTADDR寄存器中的地址,初始化发送描述符的DAV为0,接收描述符的DAV为1。

- 使能MAC和DMA模块开始发送和接收:置位ENET_MAC_CFG寄存器中的 TEN和 REN位,开启 MAC发送器和接收器。置位ENET_DMA_CTL寄存器中的 STE位和 SRE位,使能 DMA的 发送和 接收。

- 发送流程:获取发送描述符,打包数据写入描述符指向的缓存中,置位DAV,写入任意值到 ENET_DMA_TPEN寄存器中,使 TxDMA退出挂起模式,开始发送数据。如需等待数据发送完毕,有两种方法来确定当前帧是否发送完毕。第一种方法为轮询当前描述符的 DAV位直到其复位;第二种方法仅适用于当 INTC位为 1的况,应用程序可以轮询ENET_DMA_STAT寄存器的 TS位直到其置位。

- 接收流程:轮询方式:轮询查看描述符列表中的第一个接收描述符(其地址在 ENET_DMA_RDTADDR寄存器中配置);如果 RDES0的 DAV位复位,则说明描述符已被使用过,且接收缓存空间已存储了接收帧,处理接收帧数据;置位当前描述符的 DAV位,以复用当前描述符接收新的帧;继续查看列表中的下一个描述符。中断方式:在中断函数中,首先判断ENET_DMA_STAT中的RS是否置位,如果置位,则说明时接收完成中断,可以读取数据,读取数据后置位当前描述符的 DAV位,以复用当前描述符接收新的帧;两种接收方式在读取数据的过程中可以顺便检测一下DMA是否挂起了,如果挂起了就恢复一下。

5、其他

发送帧格式:一个正常的发送帧应该由以下及部分构成:前导码,帧首界定码SFD,目标地址 DA,源地址 SA QTAG前缀(可选),长度 /类型域 LT,数据 PAD填充域(可选),和帧校验序列 FCS。前导码和帧首界定码都是由MAC自动生成的,因此应用程序只需要存储目标地址,源地址,(若需要),长度 /类型,数据,填充域(若需要),帧校验序列(若需要)。DPAD位和 DCRC位用于配置填充位和帧校验序列的自动生成。

帧接收:MAC接收到的帧都会被送入RxFIFO中。MAC接收到帧后会剥离其前导码和帧首界定码,并从帧首界定码后的第一个字节(目标地址)开始向FIFO发送帧数据。

TXFIFO转发机制:在直通模式 Cut-Through 下,当 FIFO中的数据等于或超过了所设置的阈值时(或者在达到阈值之前写入了 EOF),数据会从 FIFO中取出并送入到 MAC控制器中。这个阈值可以通过 ENET_DMA_CTL寄存器的 TTHC位来设置;在存储转发模式 Store-and-Forward 下,只有当一 个完整的帧写入 FIFO之后, FIFO中的数据才会被送入 MAC控制器。但还有一种情况下,帧没有被完整写入 FIFO FIFO也会取出数据。这种情况为 TxFIFO的大小小于要发送的 以太网帧长度,那么在 TxFIFO即将全满时,数据会被送入到 MAC控制器。

RXFIFO转发机制:RxFIFO工作于直通模式时,如果 FIFO中的数据量大于门限值(可通过 ENET_DMA_CTL寄存器的 RTHC位设置),就开始从 FIFO中取出数据,并通知 DMA接收。当RxFIFO工作于存储转发模式(通过 ENET_DMA_CTL寄存器的 RSFD位设置)时, DMA只在RxFIFO完整地收到一帧后,才将其读出。此模式下,如果 MAC设置成将所有错误帧丢弃,那么 DMA只会读出合法的帧,并转发给应用程序。一旦

寄存器的 RSFD位设置)时, DMA只在RxFIFO完整地收到一帧后,才将其读出。此模式下,如果 MAC设置成将所有错误帧丢弃,那么 DMA只会读出合法的帧,并转发给应用程序。一旦文章来源:https://www.toymoban.com/news/detail-456116.html

TDES0中有两种校验:一种是插入IP包头中的校验和校验,一种是以太网帧尾的CRC校验。文章来源地址https://www.toymoban.com/news/detail-456116.html

到了这里,关于Ethercat学习-GD32以太网学习的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[工业互联-9]:EtherCAT(以太网控制自动化技术)+TwinCAT 在生产自动化控制中的应用 、](https://imgs.yssmx.com/Uploads/2024/02/476465-1.png)